作者:OpenSLee

1 背景知识

IP(Intellectual Property)在嵌入式FPGA设计中,指的是某些设计好的模块,分为软件模块和硬件模块。这些模块,一般都是已经测试好,所有功能完善的,由一些用户自己设计的。有些模块是免费的,也有收费的模块。所有用户都可以将这些IP核(IP Core)导入到自己的工程中,同样,所有用户也都可以定制自己的IP核。

将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器,SDRAM控制器,PCI接口等等设计成可修改参数的模块,让其他用户可以直接调用这些模块,这样就大大减轻了工程师的负担,避免重复劳动。随着CPLD/FPGA的规模越来越大,设计越来越复杂,使用IP核是一个发展趋势。理想地,一个知识产权核应该是完全易操作的--也就是说,易于插入任何一个卖主的技术或者设计方法。通用异步接发报机(UARTs)、中央处理器(CPUs)、以太网控制器和PCI接口(周边元件扩展接口)等都是知识产权核的具体例子。

知识产权核心分为三大种类:硬核,中核和软核。硬件中心是知识产权构思的物质表现。这些利于即插即用应用软件并且比其它两种类型核的轻便性和灵活性要差。像硬核一样,中核(有时候也称为半硬核)可以携带许多配置数据,而且可以配置许多不同的应用软件。三者之中最有灵活性的就是软核了,它存在于任何一个网络列表(一列逻辑门位和互相连接而成的集成电路)或者硬件描述语言(HDL)代码中。

2 rgb2ycbcr IP的建立

对于RGB转ycbcr的理论可参考《FPGA图像处理之rgbtogray算法的实现》。

1) 创建工程添加源文件

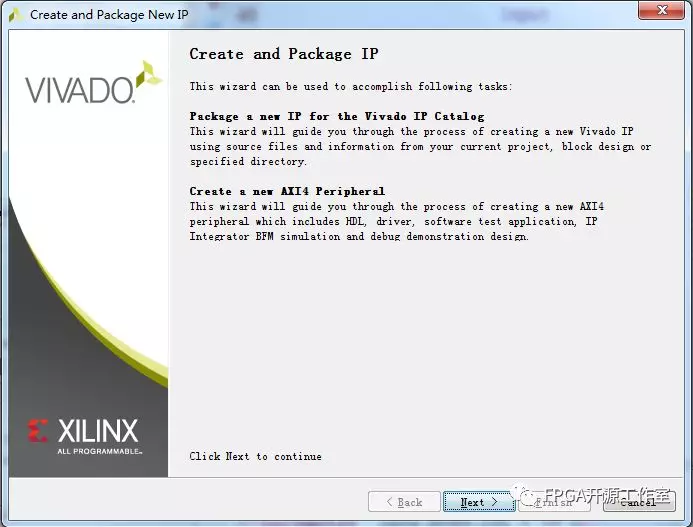

2) 点击菜单栏->tools->Create and Package New IP ->Next

3)点击package your current project->Next

4)选择IP Location 这里我们选着Include IP generated files->next->finished

IP Location 放在一个比较好找的位置,以便我们后期的使用

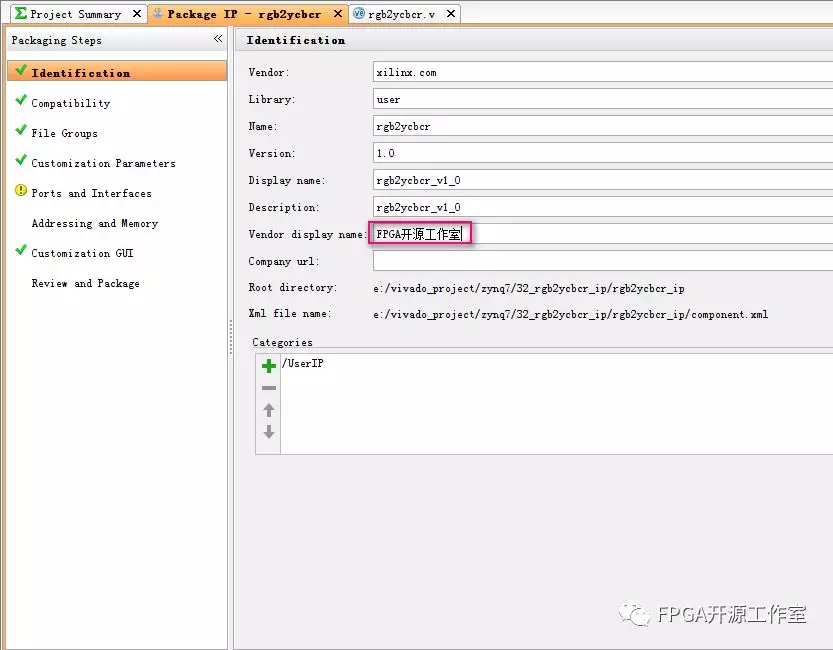

5)对IP进行封装点击

各种参数代码检测无误后点击Review and Package->Package IP

IP 封装完成,以后我们可以使用此IP进行设计。

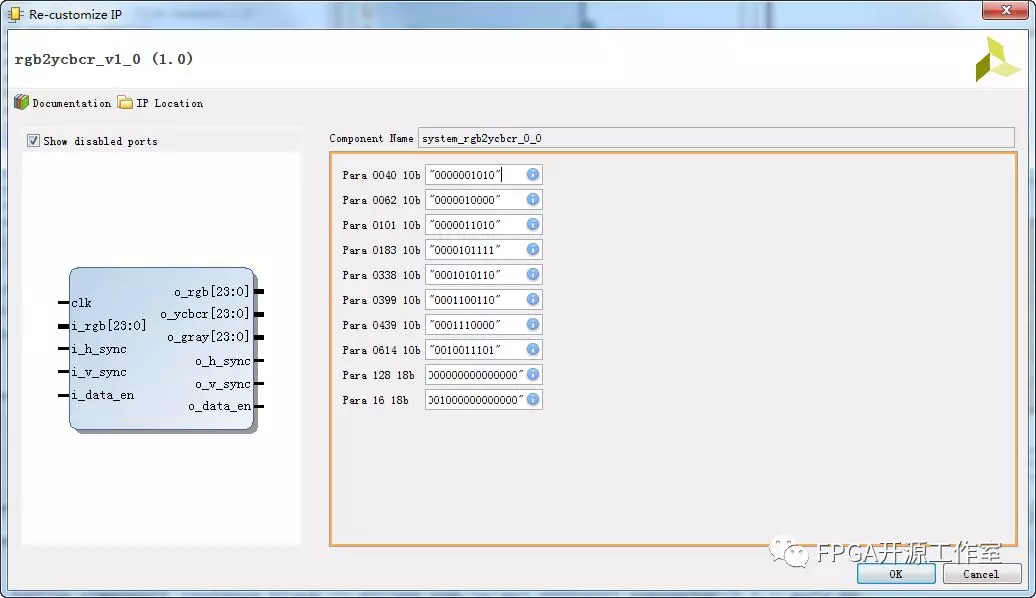

FPGA开源工作室rgb2ycbcr IP的介绍

如上图所示,clk为像素时钟,i_rgb接口为rgb888格式输入。我们分别引出了o_rgb(RGB888)、o_ycbcr和o_gray接口,完成了一个模块三种颜色空间的输出以便后期设计的使用。

3 zynq-7000的实现

利用《Zynq-7000电子相册的实现》的设计成果。我们在此平台上验证rgb2ycbcr模块。