本文是该系列的第20篇。数字水印是一种将标识信息嵌入到载体当中,且不影响载体使用的一种技术,主要分为时域水印嵌入算法(将水印嵌入到时域采样数据中)和变换域水印嵌入算法(先对音频做变换,将水印嵌入到变换域系数中)。本文将介绍一种简单的时域水印嵌入算法——LSB算法。

LSB算法

通常数字水印技术有不可感知性的要求,即嵌入数字水印后载体数据发生了变化,但是不会影响到该数据的使用,对使用者而言也不可察觉。

该算法将水印信息嵌入到数据的最低有效位(Least Significant Bit)部分,即将数据的LSB替换为需要加入的水印信息。这正是因为低位数据对整体数据的影响最小,这也导致嵌入的水印信息强度不高,否则会影响到载体的数据质量。因此该算法仅限用于脆弱性数字水印(相较于鲁棒性数字水印而言,无法承受大量失真)。

System Generator设计

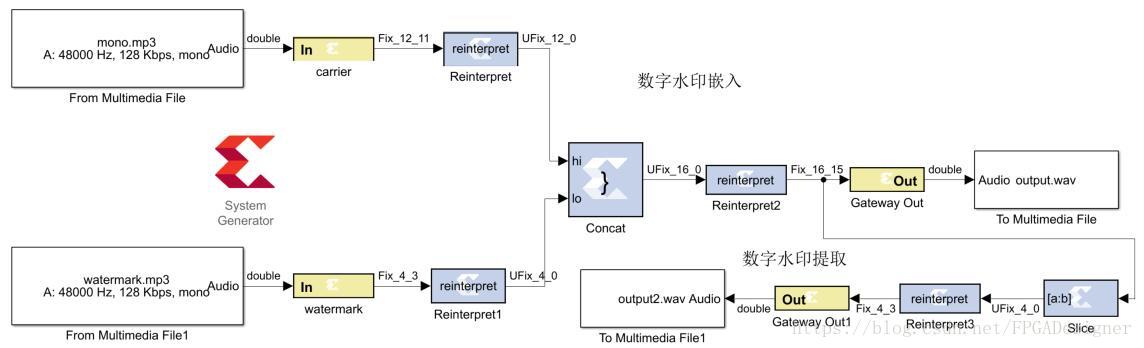

该算法的实现很简单,在Simulink中添加block按下图连接:

数字水印嵌入部分,载体数据量化为Fix_12_11格式,水印信息量化为Fix_4_3格式,这里选择两首不同的音乐作为载体和水印。使用Concat拼接两个数据,水印信息作为LSB。由于Concat模块只接收无符号整数输入,因此需要使用Reinterpret分别转换为UFix格式。Concat输出的数据再由Reinterpret转换为Fix_16_15数据,导出到wav文件中。

数字水印提取部分,直接使用slice将音频信号的低4Bits提取出即为数字水印信息。提取出的数据由Reinterpret转换为Fix_4_3,写入到音频文件中。

系统采样率为48000Hz,仿真时长10s即可。运行仿真后可以发现,播放添加了水印后的载体音乐时,完全听不出其中包含水印音乐;播放提取出的水印音乐,发现由于该算法的限制性,量化位宽较少,存在一定的噪声干扰。

block使用方法

●Concat:该block用于拼接多个比特向量,类似于Verilog语法中的“{ }”。该模块的输入只能是无符号整数,因此经常和Reinterpret(在本系列第8篇中进行过详细讲述)配合使用。该模块可以设置2~1024个输入,拼接为1个输出。

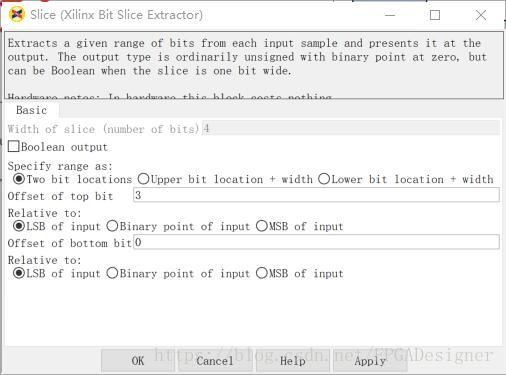

●Slice:该block用于提取输入的二进制序列中的某些位作为输出,输出格式为无符号整数。该block的配置有多种提取方式可以选择:

“Width of slice(number of bits)”设置提取出数据的位宽。当选中“Boolean output”,如果截取的位宽为单比特,输出类型会变为Boolean。

Offset of top bit和Offset of bottom bit为计算截取高位和截取低位所需的偏置值。分别有一个Relative to设置计算偏置的方式。“Specify range as”中可以选择三种提取数据的指定方式。

上面看起来比较绕,以实例的方式理解。假设输入数据IN为Fix_16_8格式,Specify range as选择Two bit location,即分别指定截取高位和截取低位:

Upper bit location+width、Lower bit location+width只需要设置截取高位或截取低位,只是截取长度由Width of slice指定。

文章来源:FPGADesigner的博客

*本文由作者授权转发,如需转载请联系作者本人