作者:小卓,来源:FPGA技术联盟

Vivado中的5种仿真模式

1、run behavioral simulation 行为级仿真,也是通常说的功能仿真

2、post-synthesis function simulation综合后的功能仿真

3、post-synthesis timing simulation综合后带时序信息的仿真,和真实运行的时序就相差不远了

4、post-implementation function simulation布线后的功能仿真

5、post-implementation timing simulation(布局布线后的仿真) 执行后的时序仿真 最接近真实的时序波形

不同仿真模式的区别

数字电路设计中一般包括3个大的阶段:源代码输入、综合和实现,而电路仿真的切入点也基本与这些阶段相吻合,根据适用的设计阶段的不同仿真可以分为RTL行为级仿真、综合后门级功能仿真和时序仿真。这种仿真轮廓的模型不仅适合FPGA/CPLD设计,同样适合IC设计。

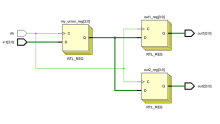

1. RTL行为级仿真

在大部分设计中执行的第一个仿真将是RTL行为级仿真。这个阶段的仿真可以用来检查代码中的语法错误以及代码行为的正确性,其中不包括延时信息。如果没有实例化一些与器件相关的特殊底层元件的话,这个阶段的仿真也可以做到与器件无关。因此在设计的初期阶段不使用特殊底层元件即可以提高代码的可读性、可维护性,又可以提高仿真效率,且容易被重用。(绝大部分设计人员将这个阶段的仿真叫功能仿真!)

2. 综合后门级功能仿真 (前仿真)

一般在设计流程中的第二个仿真是综合后门级功能仿真。绝大多数的综合工具除了可以输出一个标准网表文件以外,还可以输出Verilog或者VHDL网表,其中标准网表文件是用来在各个工具之间传递设计数据的,并不能用来做仿真使用,而输出的Verilog或者VHDL网表可以用来仿真,之所以叫门级仿真是因为综合工具给出的仿真网表已经是与生产厂家的器件的底层元件模型对应起来了,所以为了进行综合后仿真必须在仿真过程中加入厂家的器件库,对仿真器进行一些必要的配置,不然仿真器并不认识其中的底层元件,无法进行仿真。Xilinx公司的集成开发环境ISE中并不支持综合后仿真,而是使用映射前门级仿真代替,对于Xilinx开发环境来说,这两个仿真之间差异很小。

3. 时序仿真 (后仿真)

在设计流程中的最后一个仿真是时序仿真。在设计布局布线完成以后可以提供一个时序仿真模型,这种模型中也包括了器件的一些信息,同时还会提供一个SDF时序标注文件(Standard Delay format Timing Anotation)。SDF时序标注最初使用在Verilog语言的设计中,现在VHDL语言的设计中也引用了这个概念。对于一般的设计者来说并不需知道SDF

总结

行为级仿真时必须的,能够确保你所设计功能是正确的,综合后时序仿真是有必要的,能够排除大部分的时序问题,至于后仿真,只能是解决疑难杂症时再采取的大招,非常费时间,一般不建议做后仿真。

文章转载自: FPGA技术联盟