作者: OpenSLee,来源:FPGA开源工作室

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。

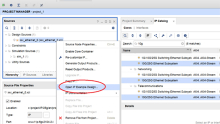

报告时钟网络命令可以从以下位置运行:

A,Vivado®IDE中的Flow Navigator;

B,Tcl命令:report_clock_networks -name {network_1}

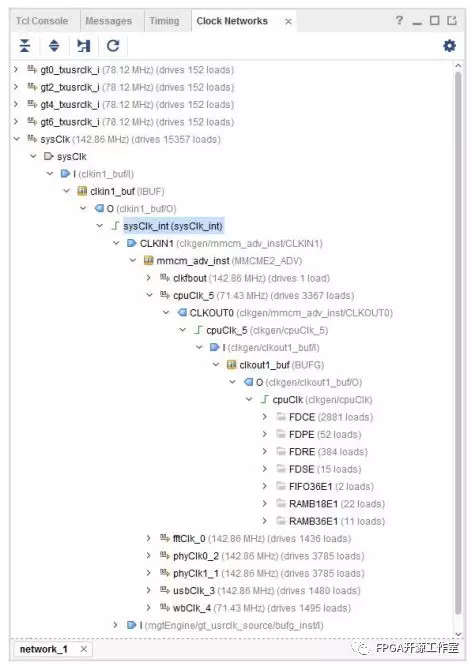

报告时钟网络提供设计中时钟树的树视图。 见图1。每个时钟树显示从源到端点的时钟网络,端点按类型排序。

图1 时钟网络

时钟树:

•显示由用户定义或由工具自动生成的时钟。

•报告从I / O端口加载的时钟。

注意:完整的时钟树仅在报告的GUI形式中详细说明。此报告的文本版本仅显示时钟根的名称。

•可用于查找驱动其他BUFGs的BUFGs。

•显示驱动非时钟负载的时钟。

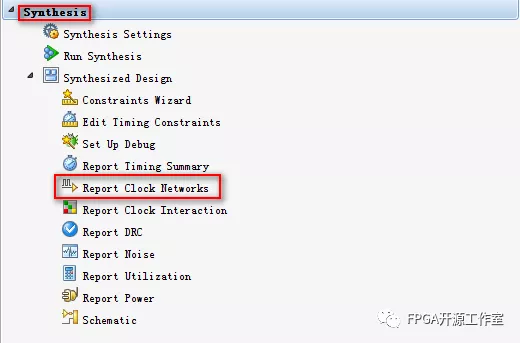

例:以vivado自带的例子wavegen为例。点击Synthesis的Report CLock Networks如图2所示。

图2 Report clock Networks

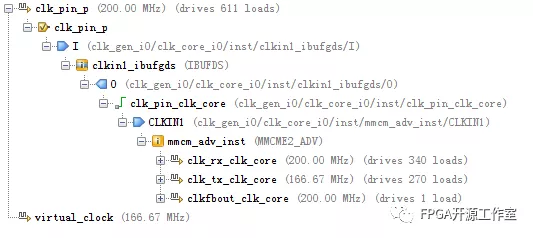

如图3所示,时钟clk_pin_p从输入引脚输入之后,经过IBUFDS,再通过MMCM生成时钟,同时显示了各个时钟的频率。如果我们未添加时钟约束,报告将显示Unconstrained(未约束的时钟,root clock).可以选中未约束的时钟右击选择Create Clock创建时钟。

图3 时钟网络

本文转载自: FPGA开源工作室