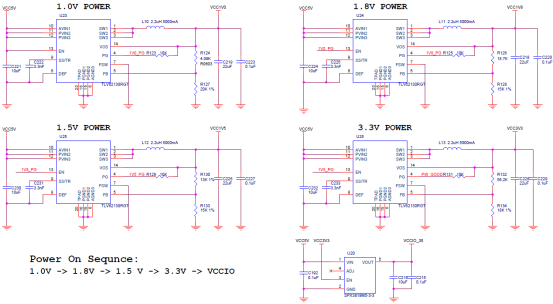

因为ZYNQ 的PS 和PL 部分的电源有上电顺序的要求,在电路设计中,按照ZYQN 的电源要求设计,上电依次为1.0V -> 1.8V -> 1.5 V -> 3.3V -> VCCIO,下图为电源的电路设计:

ZYNQ芯片的电源分PS系统部分和PL逻辑部分,两部分的电源分别是独立工作。PS系统部分的电源和PL逻辑部分的电源都有上电顺序,不正常的上电顺序可能会导致ARM系统和FPGA系统无法正常工作。

PS部分的电源有VCCPINT、VCCPAUX、VCCPLL和PS VCCO。

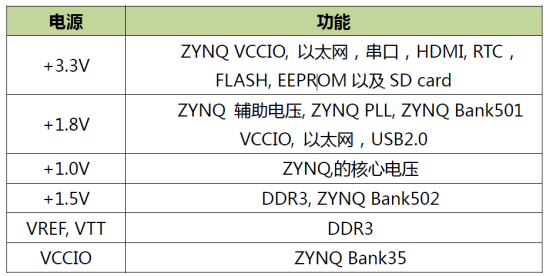

VCCPINT为PS内核供电引脚,接1.0V;

VCCPAUX为PS系统辅助供电引脚,接1.8V;

VCCPLL为PS的内部时钟PLL的电源供电引脚,也接1.8V;

PS VCCO为BANK的电压,包含VCCO_MIO0,VCCO_MIO1和VCCO_DDR,根据连接的外设不同,连接的电源电源也会不同,VCC_MIO0连接3.3V,VCCO_MIO1连接1.8V,VCCO_DDR连接1.5V。PS系统要求上电顺序分别为先VCCPINT供电,然后VCCPAUX和VCCPLL,最后为PS VCCO。断电的顺序则相反。

PL部分的电源有VCCINT, VCCBRAM, VCCAUX和 VCCO。

VCCPINT为FPGA内核供电引脚,接1.0V;

VCCBRAM为FPGA Block RAM的供电引脚;接1.0V;

VCCAUX为FPGA辅助供电引脚, 接1.8V;

VCCO为PL的各个BANK的电压,包含BANK13,BANK34,BANK35,BANK的电压连接3.3V。PL系统要求上电顺序分别为先VCCINT供电,再是VCCBRAM, 然后是VCCAUX,最后为VCCO。如果VCCINT和VCCBRAM的电压一样,可以同时上电。断电的顺序则相反。

本文转自:瓜大三哥,作者:米果不回来,转载此文目的在于传递更多信息,版权归原作者所有。