本文内容来自Xilinx 张吉帅在LiveVideoStackCon2019深圳站上的精彩分享,他将重点讨论异构计算中非常具有潜力的一部分 —— FPGA,并详细介绍赛灵思以及其技术生态合作伙伴在有关视频加速,图片转码等方面的解决方案。

文 / 张吉帅

整理 / LiveVideoStack

原文链接:https://mp.weixin.qq.com/s?__biz=MzU1NTEzOTM5Mw==&mid=2247495551&idx=1&s...

1. FPGA的优势

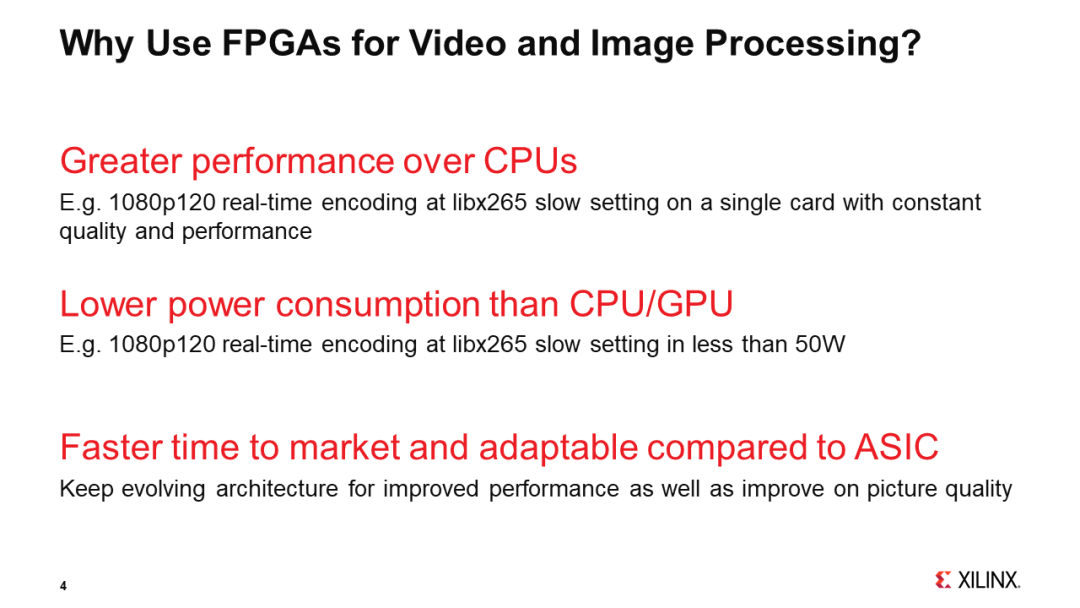

大家好,我是来自Xilinx的张吉帅,随着视频内容的火爆,其在网络上的传输量越来越大,对视频编解码算力也有了更高的需求;此外,视频压缩的标准也在不断提升,对于H.264视频编码压缩,CPU基本可以勉强支持,但对于H.265、VP9、AV1等更高的视频编码标准来说则难以胜任。根据实际数据显示,相较于CPU与GPU在BASE LAN加速卡上的表现,基于FPGA可以实现对H.265 1080P 120帧/秒的视频编码压缩,并且在压缩率、压缩质量以及功耗上都具有更大的优势。除此之外,与ASIC相比,其性价比会高于FPGA。FPGA还占有相当大一部分市场份额的原因主要是因为FPGA从方案设计开发到实际应用,整体流程周期非常短。

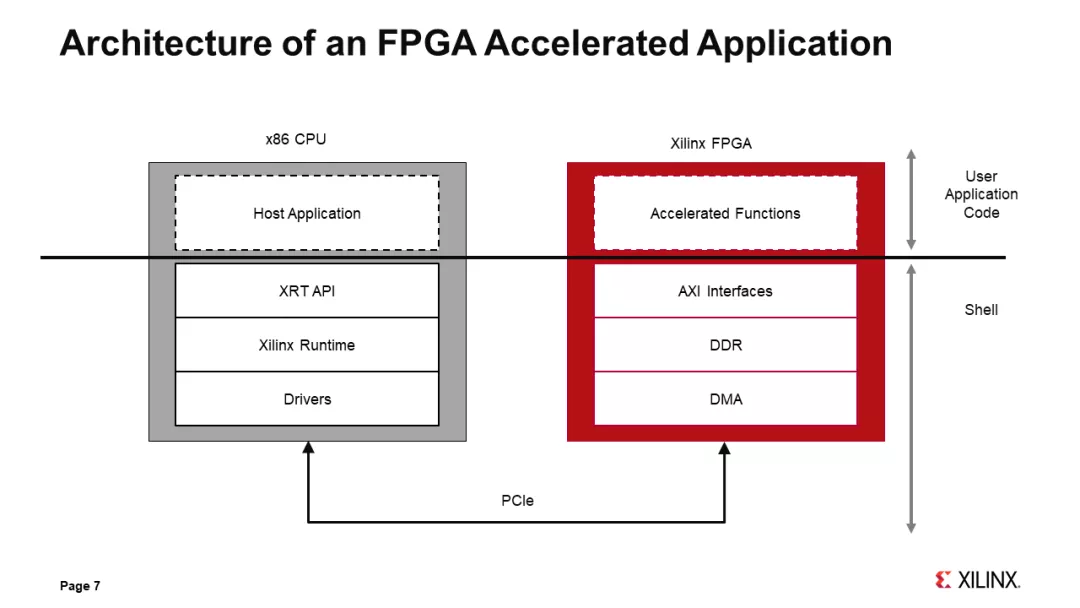

具体地说,赛灵思所提供的各种硬件加速解决方案,架构通常为FPGA+CPU的异构方式。从开发者或者应用的角度,实际CPU端包含一个应用程序,FPGA端则包含一段二进制的FPGA逻辑代码。而从使用的角度来看,只需要考虑图中横线以上部分的使用,与传统软件类似,使用起来相对简单。

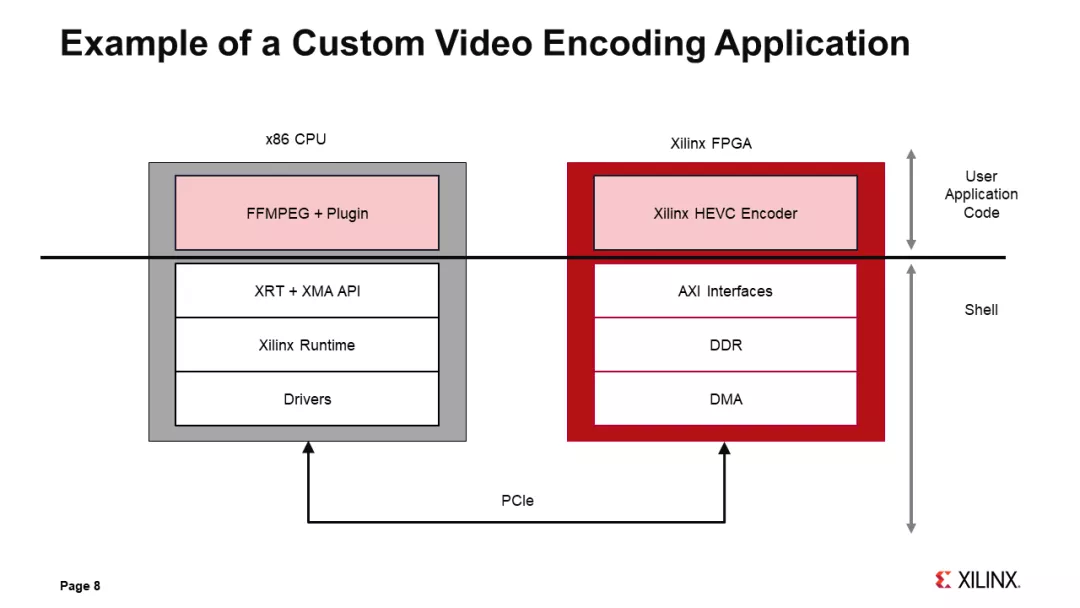

在实际应用中,FPGA部分实现的是编码相关的功能,CPU部分则是通过框架加插件的方式实现FFmpeg的应用,并且插件部分已经集成,无需开发,用户只要简单调用FFmpeg,即可使用赛灵思高性能的H.264编码器。

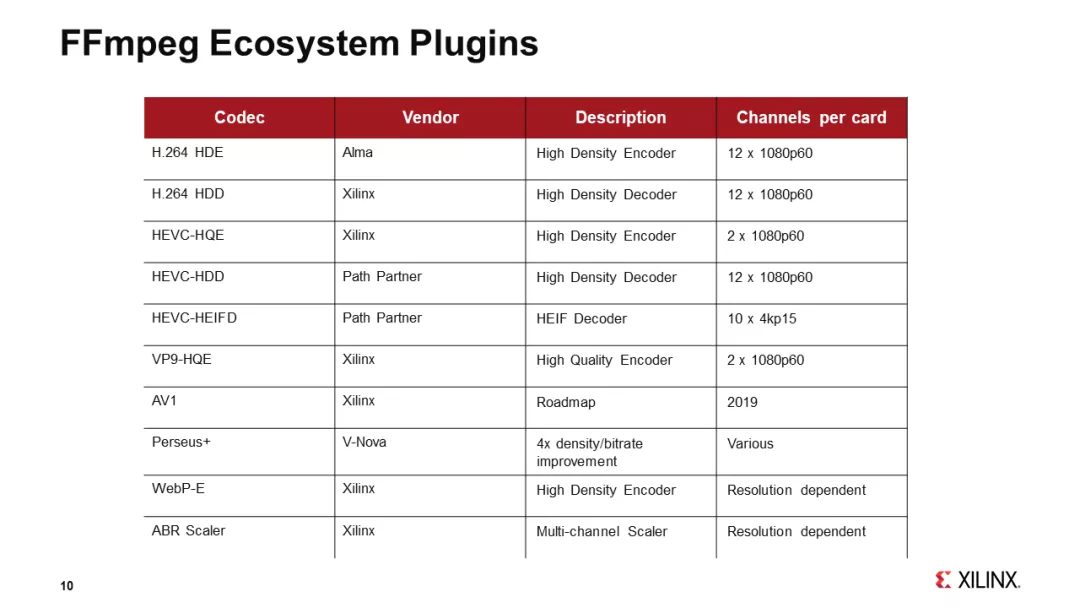

图为赛灵思H.264、HEVC、VP9、AV1等FPGA相关IP产品。FPGA异构计算的灵活性体现在我们可以将多种不同IP放入同一芯片,完成多种不同工作。例如GPU或ASIC可以实现编码相关工作,而对于赛灵思FPGA,我们可以在芯片中加入HEVC和ABRScaler的IP,从而实现多种不同码率视频流的生成。除此之外,还有低延迟等更多特性。

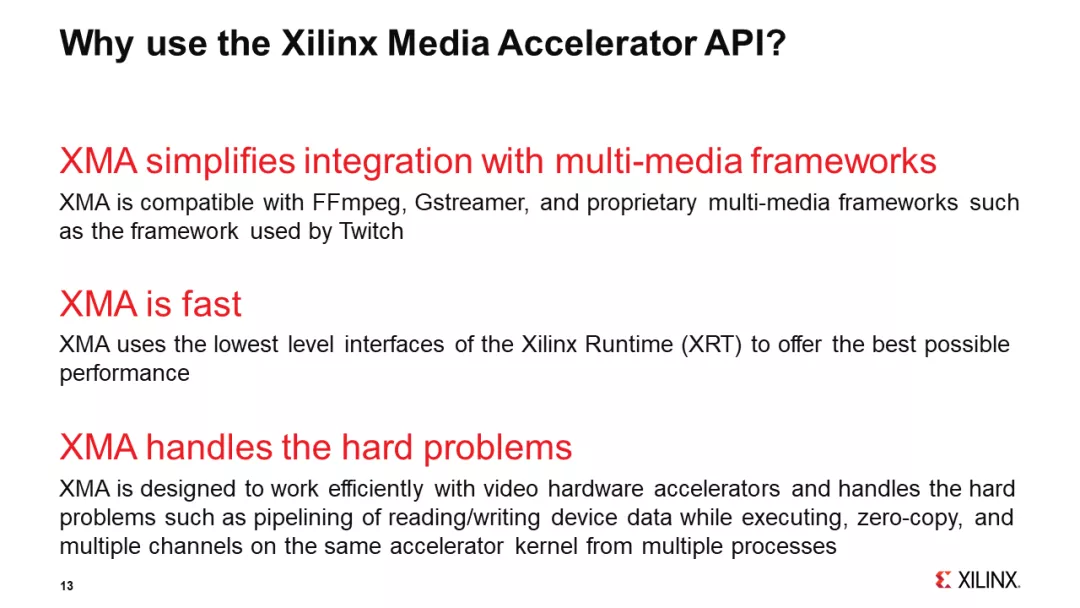

2. Xilinx Media Accelerator(XMA)

赛灵思提供了一整套的API,即Xilinx Media Accelerator(XMA),用户可以基于API完成一系列的开发。从CPU通过PCIE到赛灵思芯片,0拷贝的XMA,可以支持多线程、多进程,当然还包括刚才提到的到FFmpeg框架的接口API。

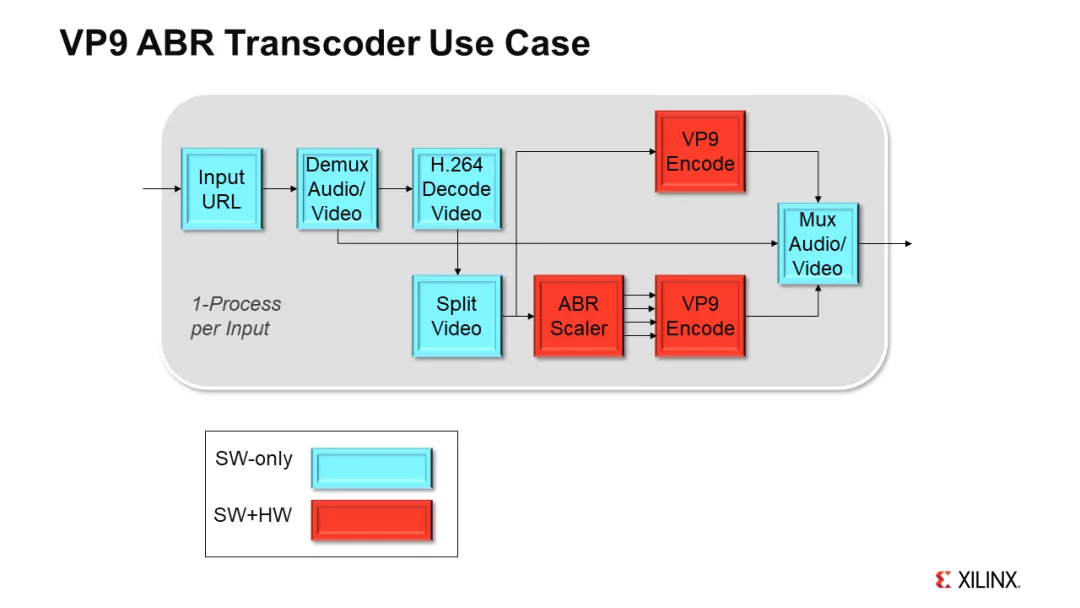

2.1 FPGA接入VP9编码器

与ASIC不同的是,赛灵思FPGA芯片可用于不同工作。例如接入的是VP9编码器,图中浅蓝色部分为CPU进行的工作,红色部分为FPGA芯片进行的工作。数据进入芯片,通过CPU完成解码,进行音频和视频的解码调试,将解码出的视频发送至ABR的IP,再将结果传递给VP9编码器,最终与音频进行调制,生成VP9编码的音视频媒体流。

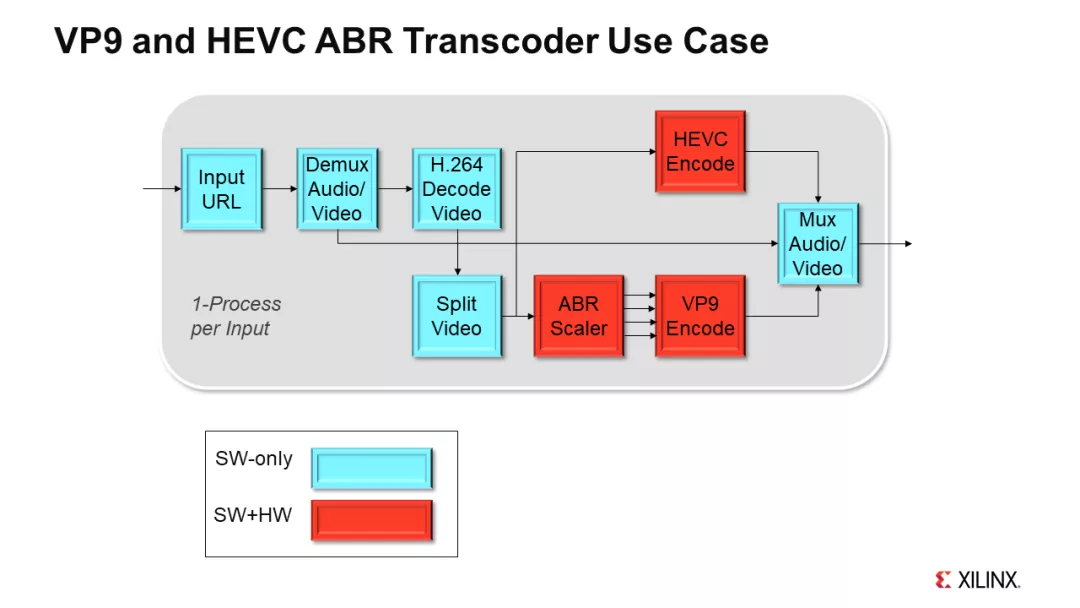

2.2 HEVC+VP9编码视频流生成

在上述方案的基础上,只需要加载HEVC的IP,即可在同一芯片中实现VP9编码视频流以及生成HEVC编码视频流。

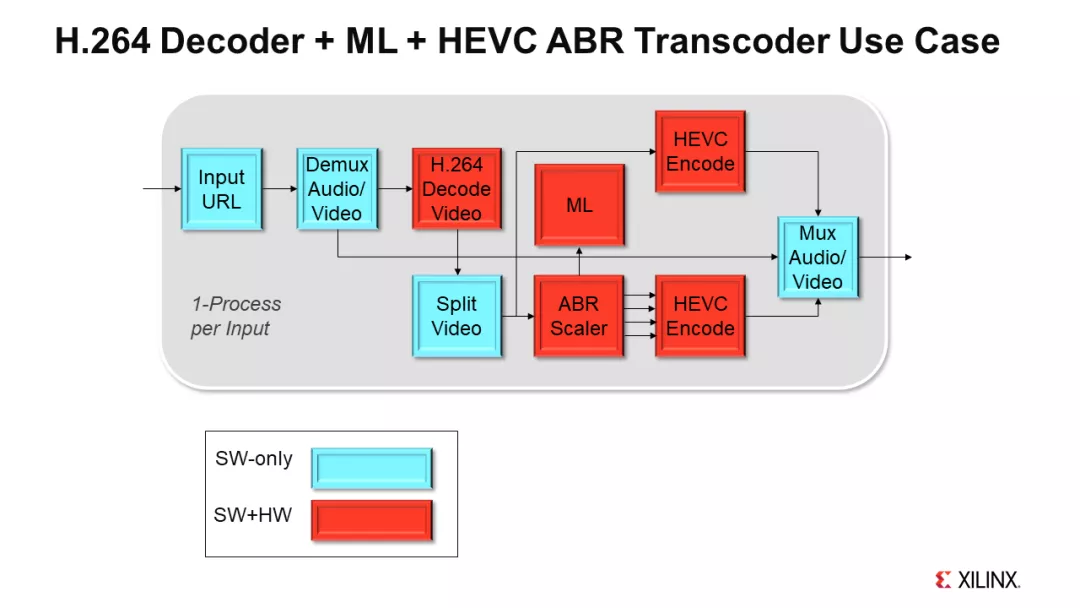

2.3 人脸识别

除此之外,如果我们希望实现视频中人脸识别的功能,还可以在其中加入Machine Learning的IP。

2.4 同一芯片中可接入多个IP

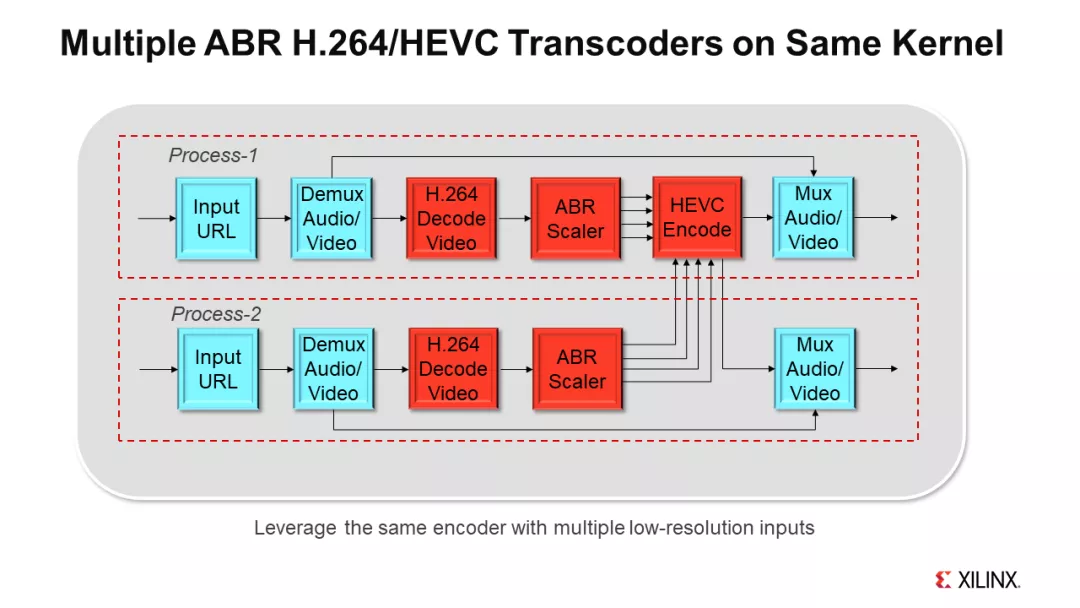

上述内容中所提到的ABR的IP,H.264的IP,在同一芯片中可以接入多个,并通过CPU进程进行调度。

编码器多路视频流输入、输出的应用

3. 赛灵思实时视频转码架构

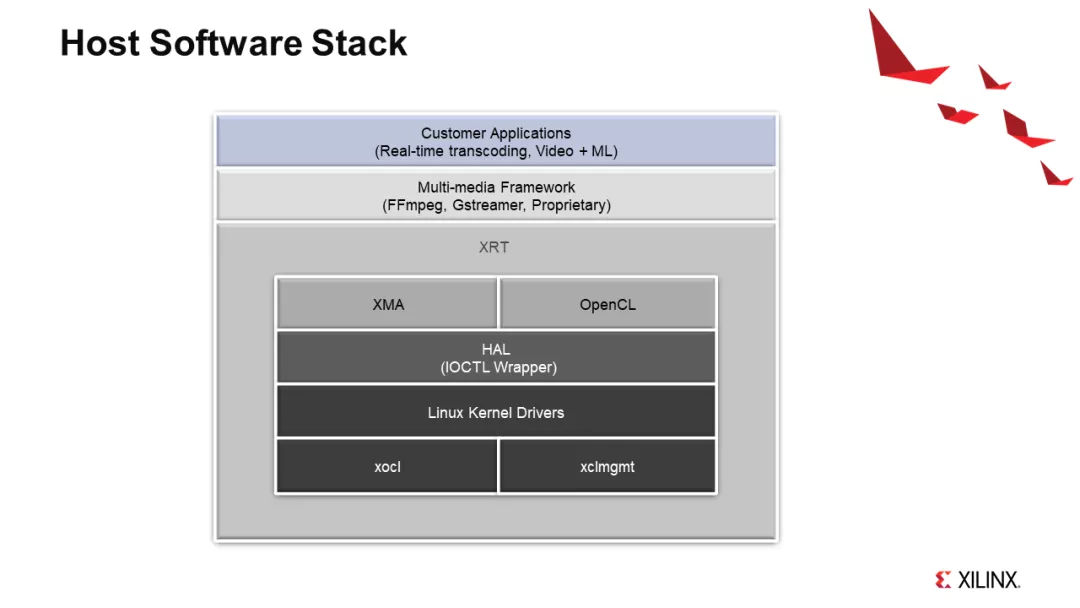

如上架构图所示,赛灵思实时视频转码包含两种不同的途径,XMA和OpenCL。按照层次结构,向下划分为HAL硬件抽象层,驱动以及最底层的数据通道和管理通道。

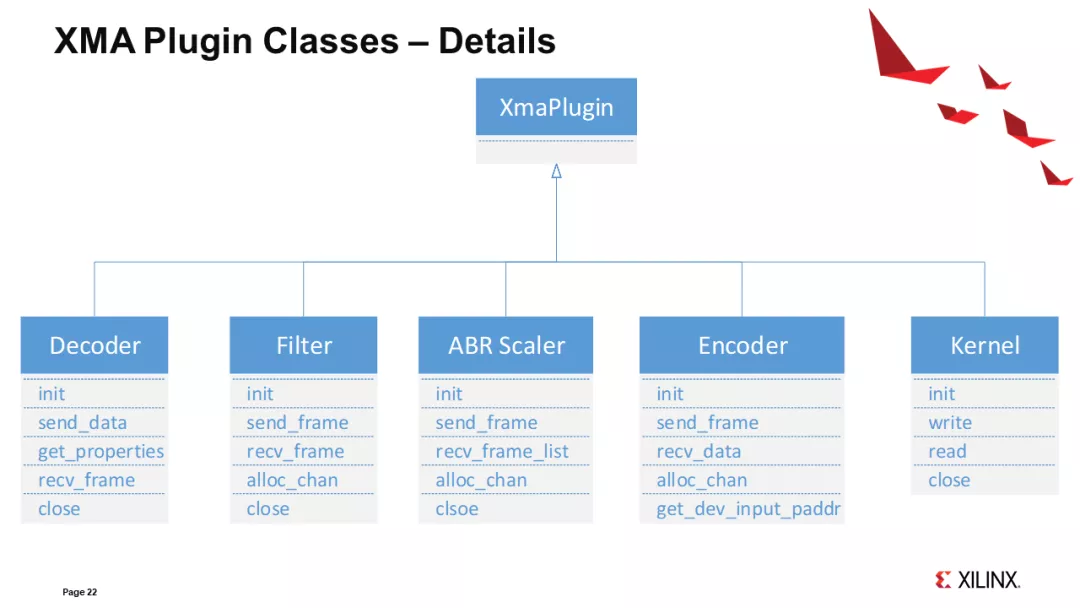

实现编码器编程所需要了解的XMA的相关API

上述XMA相关API事实上是对编码、解码等行为的抽象,因此我们可以看到基本上都是初始化的过程,即发送数据到Lower Edge,再到Video Kernel。

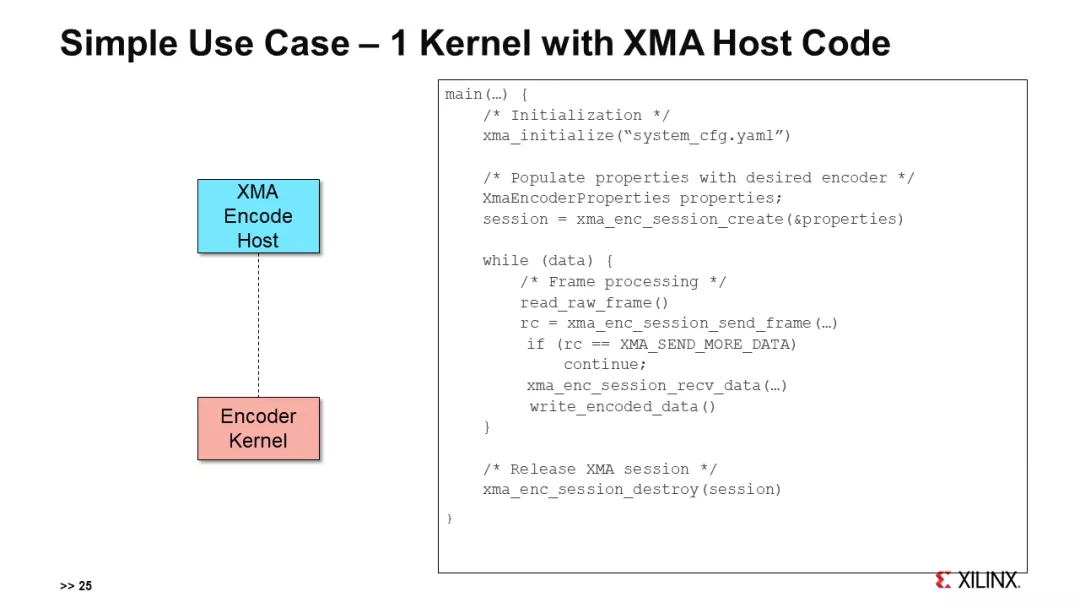

Video Kernel与芯片中相关IP接入时的代码

文末给出的参考链接,github中的代码可以直接运行

如果不需要通过FPGA开发新的功能,只是简单的使用编码器,如图左所示为传统的FFmpeg框架,如图右所示为赛灵思编码器中FFmpeg的调用。