本文转载自: XILINX开发者社区微信公众号

本文来自 XILINX 产品应用工程师 John Bieker

本文旨在提供一种方法,以帮助设计师判断给定模块是否能够在空裸片上达成时序收敛。 如果目标模块无法在空裸片上达成非关联 (OOC) 时序收敛,则恐难以与设计其余部分达成关联性时序收敛。设计师可从完整设计中提取目标模块、对其进行布局规划、约束,然后通过实现工具来运行这些模块,以判断是否能够独立达成时序收敛。

随着设计复杂性和规模的持续增加,以可重复且可靠方式达成时序收敛的难度也变得越来越高。 完全完成大型设计的布局布线所需运行时间冗长,导致难以应对期间种种状况,但对完全完成组装的设计进行时序分析时,设计师一般会发现发生的大部分时序违例都集中于少数几个关键模块。

在此情况下,如下方法很有效:可通过执行可行性分析来查看存在大量违例的模块本身在非关联实现情况下能否达成时序收敛。此分析的目的是降低完全布局布线任务的复杂性,以便帮助设计师加速迭代,从而更快找到潜在解决方案。

在本文中,我们将讲解一种常见用例,即从已布线的设计中提取出一个分层块(目标模块)进行非关联实现。

(还有一种类似的方法可用,即将此类模块标记为非关联,并对其进行综合)

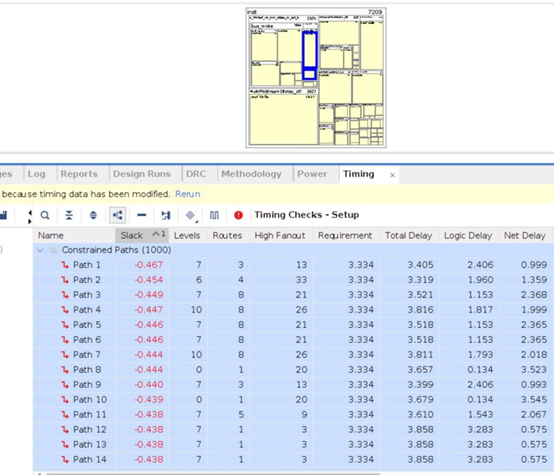

1.从已完全布线的设计中识别具有严重时序违例的模块

要直观显示可能存在时序收敛问题的模块,有效方法之一是打开已布线的设计检查点并生成一份列表,其中包含前 500-1000 个时序收敛失败的端点。

report_timing -of [get_timing_paths -max_paths 1000 -slack_lesser_than 0] -file route_paths.rpt -rpx route_paths.rpx -name route_paths

最好使用 Vivado 中的“层级 (Hierarchy)”窗口来直观显示这些路径,只需点击 F6 功能键即可轻松唤起此窗口。

由于时序路径在 Vivado 中属于对象,因此可在“时序 (Timing)”窗口中将其选中,这样即可在“Hierarchy”视图中高亮显示对应的单元/信号线。 高亮显示的模块中包含的时序违例最多。

这些模块最适合使用此方法来进行分析。

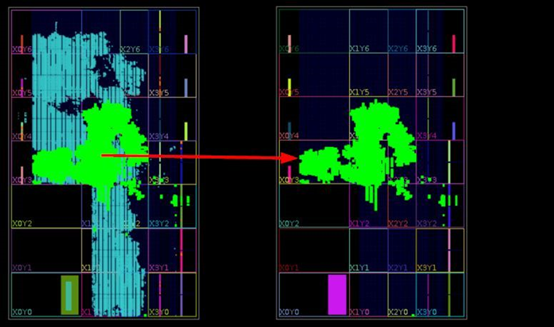

2. 提取目标模块

可使用 Tcl 命令 write_checkpoint 从已布线的设计检查点中提取目标模块。 检查点将包含布局布线信息以及限定于目标模块层级下的模块范围内的所有时序断言和时序例外(包括多周期路径、伪路径等)。

先取消 target_module.dcp 的布局布线,随后,即可对其进行非关联布局布线。

write_checkpoint -quiet -force -cell [get_cells $target_module] target_module.dcp

从已布线的检查点提取目标模块

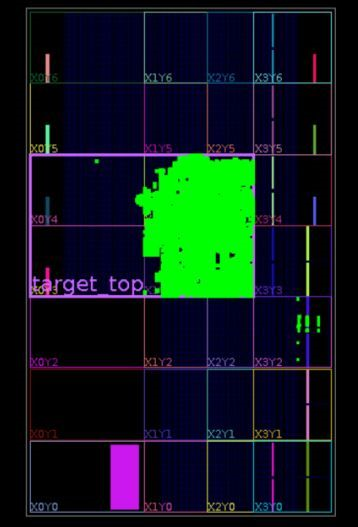

3. 创建简单的布局规划

为避免布局器将目标模块散布于整个裸片上,最好创建 1 个 Pblock 以生成该模块在完整设计上的布局方式的镜像。

以下是 floorplan.tcl 文件的示例。

# 移除现有 Pblock

if {[llength [get_pblocks]]} {

delete_pblocks [get_pblocks *]

}

# 创建 Pblock 以生成完整设计中的目标模块布局的镜像

create_pblock target_top

resize_pblock target_top -add CLOCKREGION_X0Y3:CLOCKREGION_X2Y4

add_cells_to_pblock target_top -top

目标模块布局规划

4. 创建一组简单的时序约束

此步骤将基于连接到模块的顶层时钟来创建一组时钟约束。 在目标检查点中将保留范围限定于目标模块中所含模块的时序例外。 为便于操作,最好将所有时钟强制设置为异步。 以下提供的脚本用于:

创建时钟

创建时钟间的时序例外

创建 HD.CLK_SRC 属性以便工具更准确计算时钟偏差

在每个时钟上添加 250 ps 的建立时间不确定性,以提高分析的真实性

要创建约束,请在 Vivado GUI 中选中模块并运行脚本以创建名为 constraints.tcl 的文件,此文件将用于驱动模块的非关联实现。

set CONSTRAINT_FILE [open constraints.tcl w]

set index 0

foreach pin [get_pins -filter {DIRECTION == IN} -of [get_selected_objects]] {

if {[llength [set clock [get_clocks -quiet -of $pin]]] != 0} {

set clk_name [get_property REF_PIN_NAME $pin]

puts $CONSTRAINT_FILE "create_clock -quiet -name $clk_name -period [get_property PERIOD $clock] \[get_ports $clk_name\]"

puts $CONSTRAINT_FILE "set_clock_groups -quiet -async -group \[get_clocks $clk_name\ -include_generated_clocks]"

puts $CONSTRAINT_FILE "set_property -quiet HD.CLK_SRC BUFGCTRL_X0Y${index} \[get_ports $clk_name\]"

incr index

}

}

puts $CONSTRAINT_FILE "set_clock_uncertainty -quiet 0.250 -setup \[get_clocks\]"

close $CONSTRAINT_FILE生成的 constraints.tcl 文件如下所示:

create_clock -quiet -name clk_out1 -period 20.001 [get_ports clk_out1] set_clock_groups -quiet -async -group [get_clocks clk_out1 -include_generated_clocks] set_property -quiet HD.CLK_SRC BUFGCTRL_X0Y0 [get_ports clk_out1] create_clock -quiet -name clk_out4 -period 3.334 [get_ports clk_out4] set_clock_groups -quiet -async -group [get_clocks clk_out4 -include_generated_clocks] set_property -quiet HD.CLK_SRC BUFGCTRL_X0Y1 [get_ports clk_out4] create_clock -quiet -name clk_p -period 1.389 [get_ports clk_p] set_clock_groups -quiet -async -group [get_clocks clk_p -include_generated_clocks] set_property -quiet HD.CLK_SRC BUFGCTRL_X0Y2 [get_ports clk_p] create_clock -quiet -name dphy_clk_200M -period 5.000 [get_ports clk_200M] set_clock_groups -quiet -async -group [get_clocks clk_200M -include_generated_clocks] set_property -quiet HD.CLK_SRC BUFGCTRL_X0Y3 [get_ports clk_200M] set_clock_uncertainty -quiet 0.250 -setup [get_clocks]

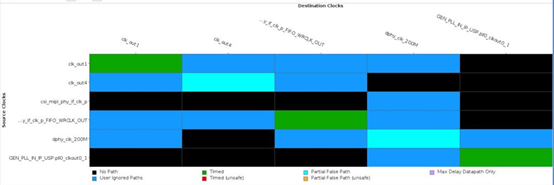

时钟交互报告会显示时钟内路径的时序安全,而时钟间的时序路径将被忽略。 这正是此分析方法的目标,因为目标模块中大部分时序路径都属于时钟内部路径。

时钟交互报告

5. 以非关联方式实现目标模块

使用以下脚本构建非关联目标模块:

open_checkpoint target_module.dcp source constraints.tcl source floorplan.tcl route_design -unroute place_design -unplace place_design write_checkpoint -force place.dcp report_utilization -file util.rpt report_timing_summary -file placed_tim.rpt report_design_analysis -timing -logic_level_distribution -of_timing_paths [get_timing_paths -max_paths 10000 -slack_lesser_than 0] -file place_vios.rpt report_timing -of [get_timing_paths -max_paths 1000 -slack_lesser_than 0] -file place_paths.rpt -rpx place_paths.rpx route_design write_checkpoint -force route.dcp report_timing_summary -file route_tim.rpt report_design_analysis -timing -logic_level_distribution -of_timing_paths [get_timing_paths -max_paths 10000 -slack_lesser_than 0] -file route_vios.rpt report_timing -of [get_timing_paths -max_paths 1000 -slack_lesser_than 0] -file route_paths.rpt -rpx route_paths.rpx report_qor_suggestions -file route_rqs.rpt write_qor_suggestions -force -tcl_output_dir route_wqs route_wqs.rpt

实现的目标模块

6. 分析并调整

完成实现运行后,即可分析时序、调整时序约束、实施布局规划并快速重复此流程,以判定模块是否能够独立达成时序收敛,然后在设计其余部分中以关联方式来实现模块。

通过使用此方法,设计师即可快速识别并解决时序瓶颈,从而缩短完整设计的时序收敛任务所需的时间。