描述

在 Vivado 2021.1 中,Control, Interfaces and Processing System (CIPS) IP 架构已重新设计。此次升级支持将来自其它 Versal 系列的器件集成到 CIPS IP 内。

如需了解升级后需用户干预的更改的相关信息,请参阅以下“升级至 CIPS 3.x”部分。

解决方案

升级至 CIPS 3.X

升级至 CIPS 3.x 及更高版本的过程是依据《Vivado Design Suite 用户指南:采用 IP integrator 设计 IP 子系统》(UG994) 中的“第 11 章:为新版本更新设计”中记录的典型 IP integrator 升级流程来执行的。

本节详述了升级期间的必要注意事项。

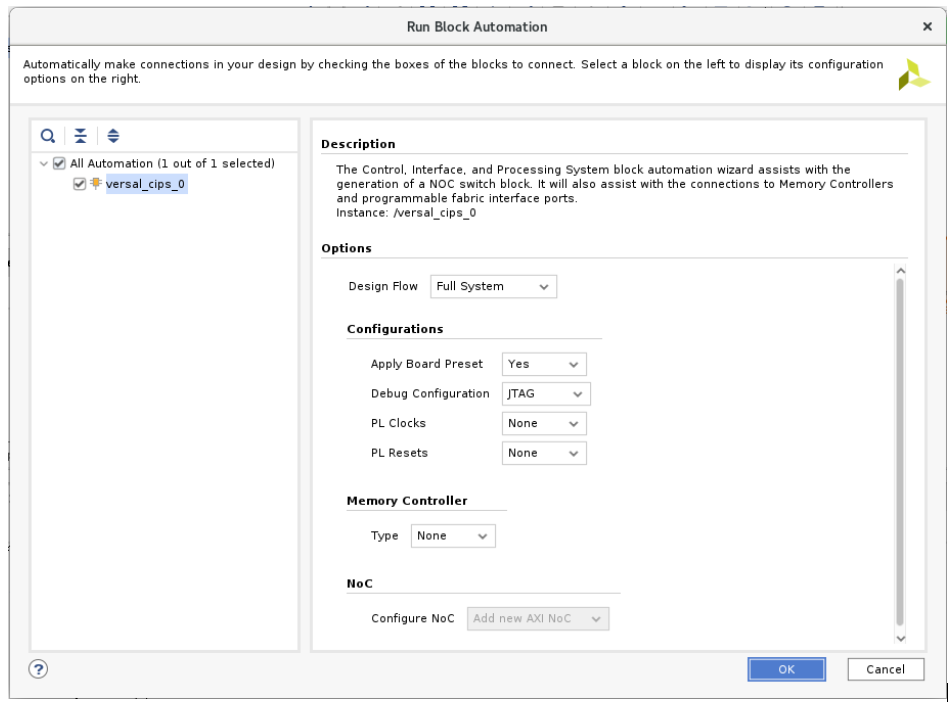

确定设计流程

现已提供“设计流程 (Design Flow)”设置以简化流程复杂性。

1. 打开 CIPS IP,并选择相关的设计流程:

地址分配已清除

地址范围已重新组织。原先版本中的“地址编辑器 (Address Editor)”中已选中的地址范围分配现在将变为未分配状态。

使用“Address Editor”中的“全部分配 (Assign All)”按钮或者使用 assign_bd_address Tcl 命令即可自动选择地址分配。定制地址范围的已分配或未分配设置必须重新输入。

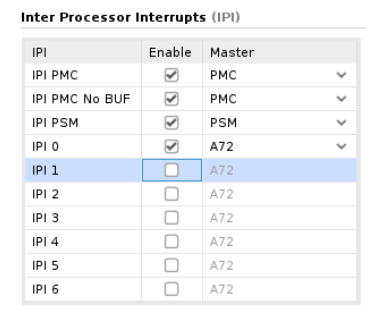

处理器间中断 (Inter Processor Interrupt) 要求

要为 APU 上运行的 2021.1 及更高版本的软件库添加增强功能,需要启用从 PMC 到 APU 的处理器间中断 (Interprocessor Interrupt)。

否则可能发生以下启动错误:

XPlmi_IpiDispatchHandler: Error: Unhandled IPI received

在“Design Flow”中:选中“Full System”,确认“PS PMC-->Interrupts--> Inter Processor Interrupts (IPI) --> IPI 0”是否已启用且设为 A72

注:此条目在 CIPS 升级期间未设置。

注:此条目通常将由 VCK190/VMK180 评估板预置及其它赛灵思提供的示例进行设置。

基于脚本的设计移植流程

如果用户使用 Tcl 脚本来维护模块框图,那么通常应通过 Vivado GUI 来为此版本完成移植。用户维护脚本的流程如下:

1. 在原先使用该模块框图的 Vivado 版本中将其打开。通常方法是使用 source 命令从 Vivado 中找到 Tcl 脚本。

2. 在新版本的 Vivado 中打开此设计,并遵循上述基于工程的移植流程进行操作,例如重新分配地址范围

3. 使用 write_bd_tcl 命令重新导出模块框图 Tcl

CIPS IP 参数格式变更:

针对每个主要的 CIPS 模块(例如,PS/PLM 和 CPM),CIPS IP 设置已从个别参数组合为单一 TCL 列表。

2020.3 及更低版本:

CONFIG.PMC_QSPI_PERIPHERAL_ENABLE {1} \CONFIG.PMC_SD0_PERIPHERAL_ENABLE {1} \2021.1 及更高版本:

CONFIG.PS_PMC_CONFIG {PMC_QSPI_PERIPHERAL_ENABLE 1 PMC_SD0_PERIPHERAL {{ENABLE 1} }新增功能特性/功能特性更新

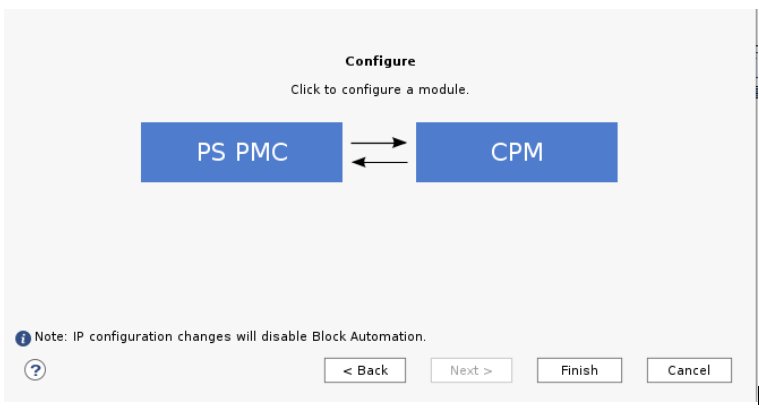

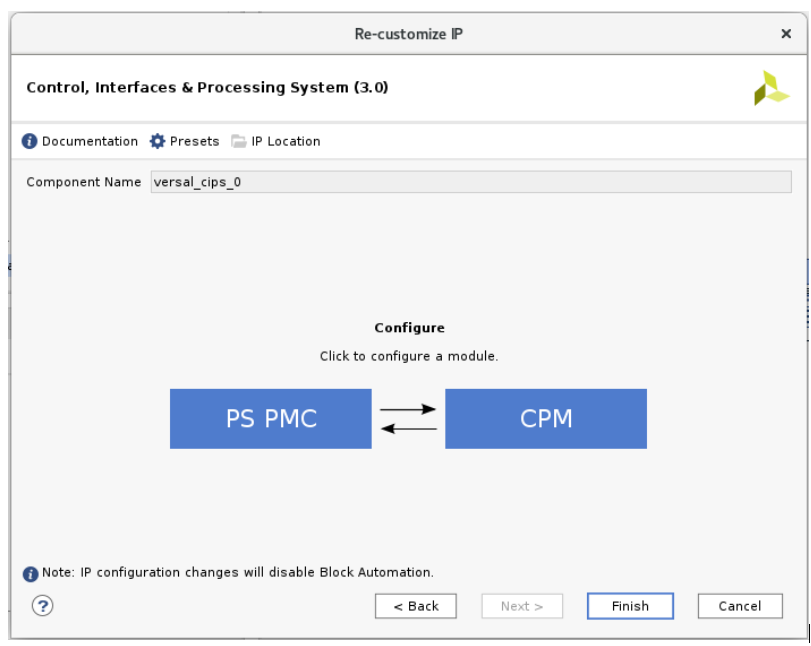

模块

CPM 和 PS PMC 设置已拆分为独立模块。单击“PS PMC”或“CPM”块即可访问各项设置。

块自动化设置功能

在块自动化设置中,现已支持 LPDDR4。

CPM 自动化设置已被暂时移除。

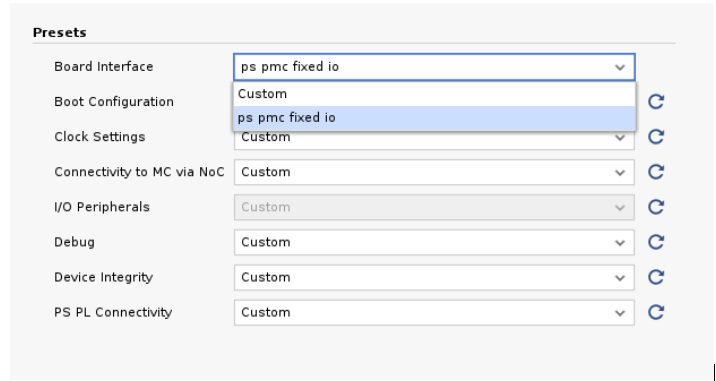

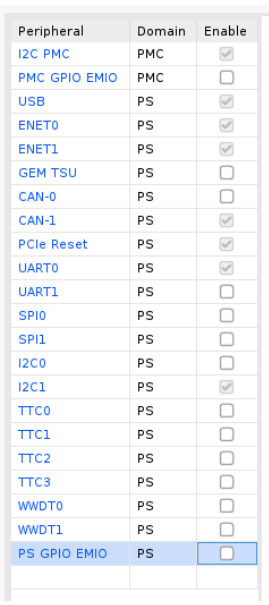

预置

“预置 (Presets)”字段允许选择预配置的设置。

预置中的“开发板接口 (Board Interface)”设置可用于从选定的开发板文件导入 IP 设置并防止对其进行修改:

要修改评估板设置,请将预置的“Board Interface”设置还原为“Custom”。

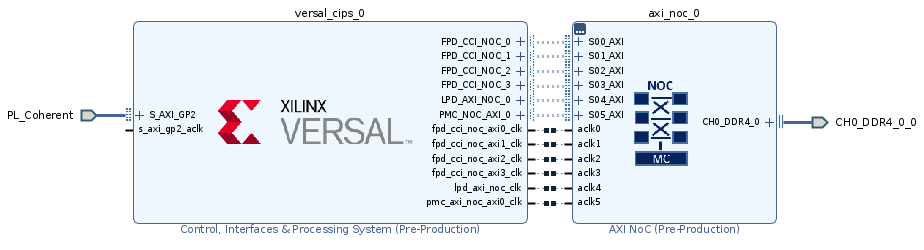

AXI 接口桥接

接口桥接现已支持 AXI 地址路径通过 CIPS 块进行传输。默认禁用接口路径通过 CIPS 进行传输。对于互连拓扑结构(例如,从 AXI 从接口通过 CIPS CCI-500 到 DRAM 的 PL 高速缓存一致性),则需要使用接口桥接,如以下 AXI 接口拓扑结构中所示:

欲知详情,请参阅(赛灵思答复记录 76566)

IP 默认设置

有多项参数默认设置已发生更改。

系统监控器电压篡改响应

“系统监控器电压篡改响应 (Sysmon Voltage Tamper Response)”已被暂时移除,计划将在 Vivado 2021.2 中重新启用。