作者:Charles Xu,本文转载自: Ingdan FPGA微信公众号

本文主要包含MultiBoot的功能简介、流程介绍和工程实现几个部分的讲解。

我们先从它的功能介绍讲起来;MultiBoot功能是大部分Xilinx FPGA可以实现的固有特性;其主要优点如下所示:

1、我们可以把多个bitstream存储在配置Flash中,通过MultiBoot功能来实现多个bitstream之间的动态切换,从而达到使用FPGA来实现多种任务;

2、在一个工程里面实现多个功能模块,而每个功能模块不需要同时运行的情况,可以通过MultiBoot功能使用相对小规模的FPGA来实现其功能,从而提高性价比;

3、MultiBoot和Fallback可以支持实现FPGA远程在线升级,当升级bit有错误可以触发Fallback来返回到Golden Image去正常运行。

Golden Image里面正常会包含FPGA实现的基本功能,例如外设配置和初始化、远程升级等等客户需要的基本功能;如果Golden Image损坏的情况下,FPGA是无法工作的,需要返回工厂重新手动烧写bit文件到Flash中。

Golden Image设计要求主要包含下面几点:

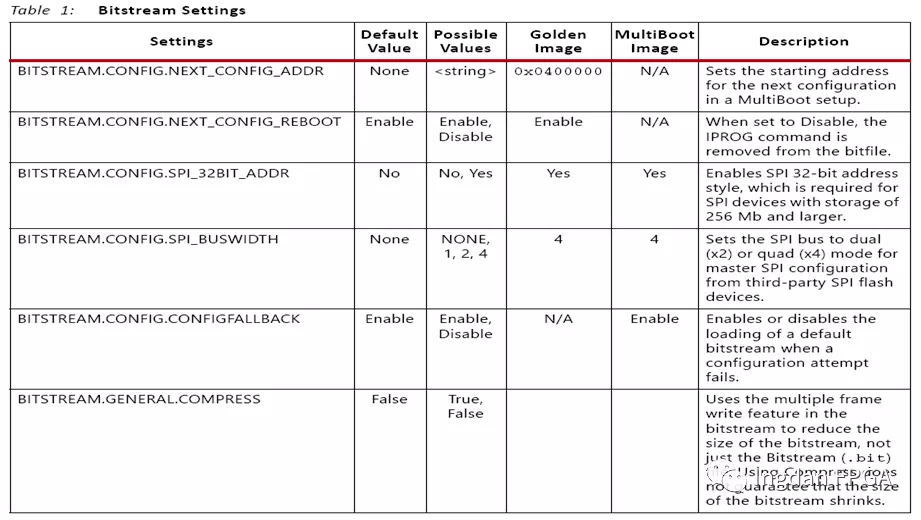

1、IPROG(Internal program) command在Golden Image里面可以通过设置bitstream setting里面的next configuration address (BITSTREAM.CONFIG.NEXT_CONFIG_ADDR),或者在HDL代码使用ICAPE3原语来设定加载地址值;通过设置BITSTREAM.CONFIG.NEXT_CONFIG_REBOOTDISABLE来把

IPROG command关掉,在这种情况下上电后会直接去加载Golden Image;

2、跳转地址寄存器WBSTAR(warm boot start address)可以在bitstream或者ICAP里面来设定;

3、MultiBoot Image必须存储在WBSTAR设置的Flash地址位置;

4、Watchdog timer包含configuration monitor和user logic monitor两种模式;在配置模式下面,Timer times out情况下,配置电路会去加载fallback bitstream。Watchdog Timer可以在bitstream options里面使能。

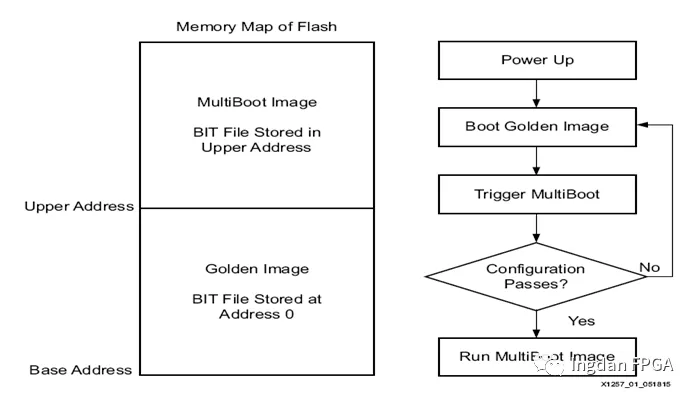

Golden Image是从Flash中的0地址开始存储;其帧头会包括WBSTAR(next_config_addr)寄存器里面指定的upper address space等信息。FPGA器件上电后会从0地址开始加载Golden Image后,会根据里面的设定来决定加载Golden Image还是直接跳转到MultiBoot Image存储地址去执行MultiBoot Image;当MultiBoot Image加载时候遇到错误,Fallback电路会触发去重新从0地址去加载Golden Image。其流程如图所示:

MultiBootImage是从设定好的upper address space去加载运行;如果加载出现问题,Fallback电路会去加载Golden Image。我们可以在Golden Image里面去修复Multiboot Image里面的错误等等问题。所以说MultiBoot Image里面运行的就是我们要实现的具体业务功能,可以是多个Multiboot Image。

Golden Image设计要求主要包含下面几点:

1、WBSTAR里面的值要指向MultiBoot存储位置;

2、Watchdog Timer功能要bitstream options里面使能;

3、代码里面可以通过IPROG命令去运行ICAPE3来跳转想要运行其他的MultiBoot Image。

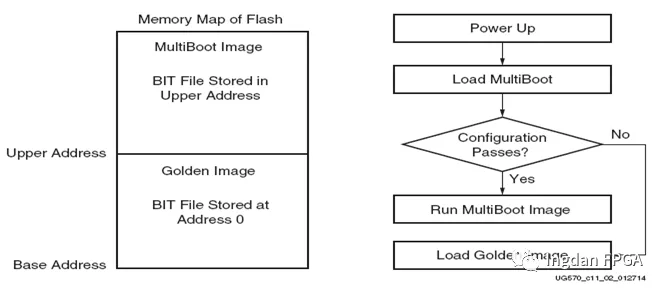

MultiBoot加载流程如图所示:

在配置过程中遇到IDCODE error、CRC error、Watchdog timer timeout error、BPI address wraparound error情况会触发fallback。Fallback功能可以通过使能bitstream.config.configfallback enable里面的ConfigFallback选项来实现。当fallback运行时,Watchdog Timer\IPROG是disable的;另外当fallback重新配置FPGA出错情况下,配置电路会停止工作同时会把INIT_B\Done保持为低电平。

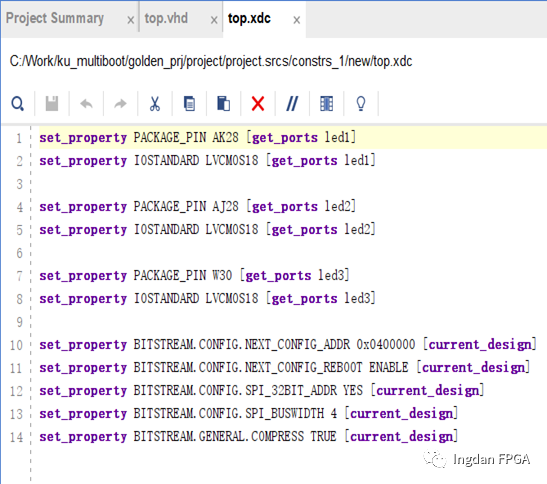

MultiBoot功能可以通过设置下面bitstream里面的参数来实现。这些参数可以通过Tcl console或者写入到XDC文件里面来实现其功能。

在前面介绍其功能作用和含义等等后,下面我们开始工程实现。

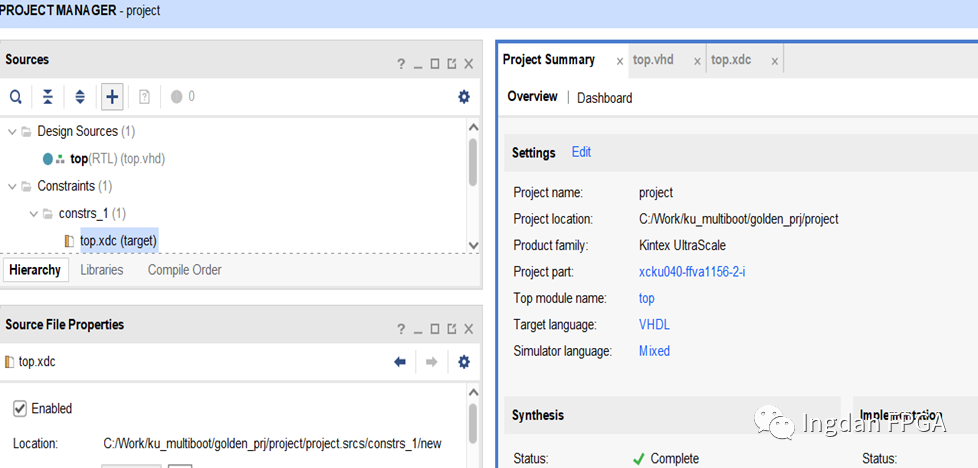

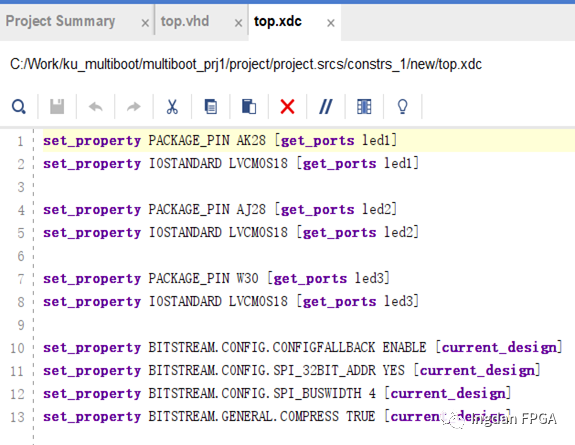

本人使用Vivado版本为2020.2;硬件基于米联客设计的KU040板卡。先建立Golden Image的工程,里面包括HDL文件和XDC约束。

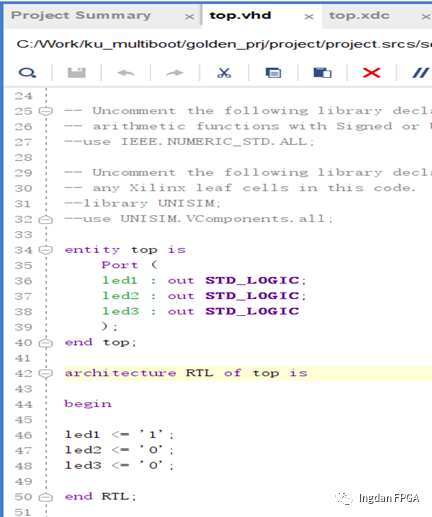

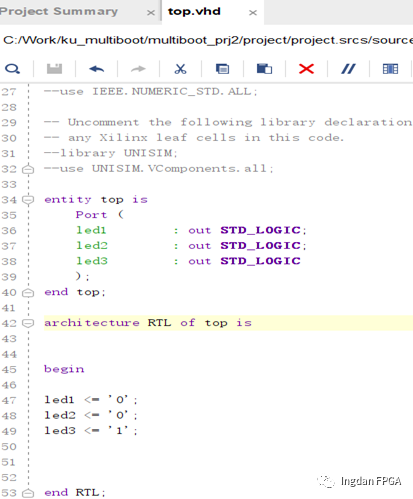

Golden Image的工程里面代码主要是把led1灯点亮。XDC里面包括IO约束信息等等,其中0x040000是Multiboot Image存放Flash里面的物理地址。

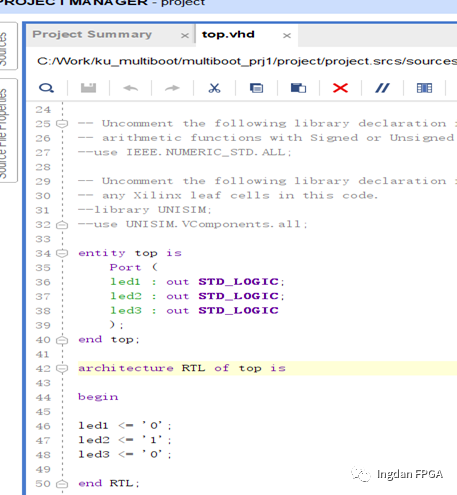

Multiboot Image led2的工程里面代码主要是把led1灯点亮。XDC里面包括IO约束和配置约束信息等等,可以看到是和Golden Image工程里面约束是有差异的。

在工程建立完成后开始合并bit文件并烧入到板卡里面:

1、使用下面tcl去把两个bit文件合为一个mcs文件;

2、通过Hardware Manager去烧入到板卡的Flash中;

3、烧写完成后选择Boot from Configuration Memory Devive去加载FPGA。

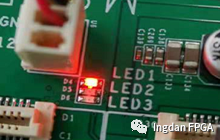

4、在FPGA加载后可以看到板卡上面LED2灯点亮。

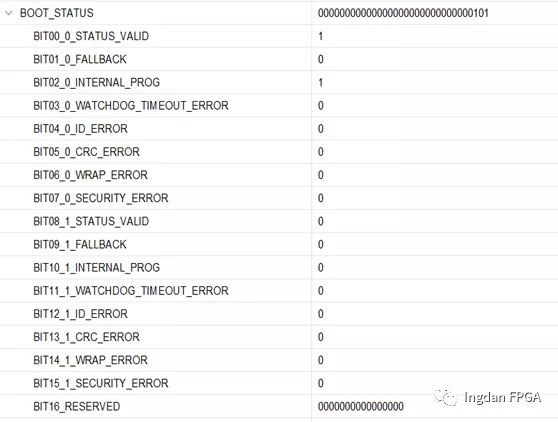

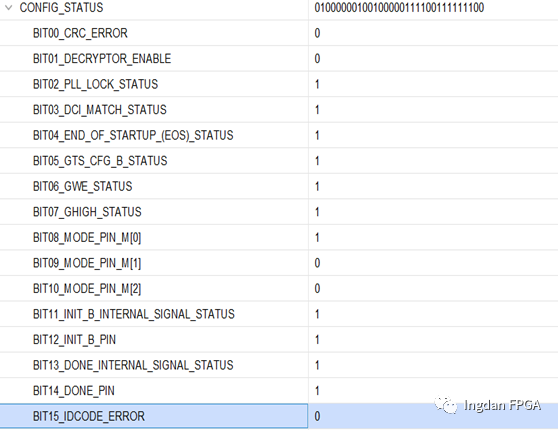

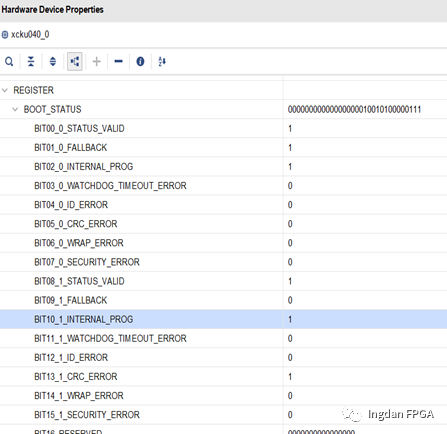

5、在Hardware Device Properties的BOOT_STATUS里面可以看到INTERNAL_PROG使能;由于加载没有错误,目前运行的是Multiboot程序。CONFIG_SATUS里面可以看到DON_PIN拉高。

下面我们尝试把multiboot image里面的IDCODE修改掉,人为的造成错误来验证板卡是否会跳转到Golden Image去执行。

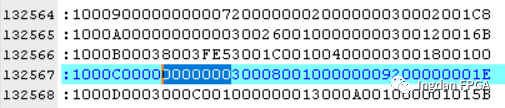

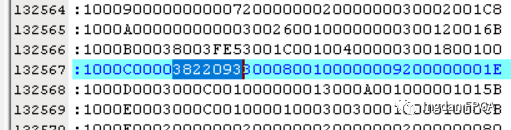

1、使用UltraEdit把ku_multiboot_spix4.mcs打开后,搜索到Update.bit里面的KU040的IDCODE3822093,并把它修改为0;重新生成ku_multiboot_spix4 _id.mcs文件烧入到FPGA.

2、按照前面流程合成bit文件后烧入到Flash中并上电;

3、在FPGA加载后可以看到板卡上面LED1灯点亮;证明Fallback功能生效,当Multiboot Image损坏后可以安全加载Golden Image。

4、在Hardware Device Properties的BOOT_STATUS里面可以看到INTERNAL_PROG使能,ID_ERROR拉高;这时候Multiboot Image加载遇到ID错误,FPGA返回到Golden Image去运行。

我们可以再尝试把multiboot image其他部分破坏掉导致CRC出错来验证功能。

1、使用UltraEdit把ku_multiboot_spix4.mcs打开后,在Update.bit里面做如下修改来验证CRC错误情况。

2、烧入到板卡上电后;由于multiboot image里面有CRC错误,所以板卡还是返回到Golden Image去运行。

除了前面我们在bitstream里面去实现Multiboot功能,我们还可以在代码里面嵌入IPROG的命令来实现Image的跳转功能。

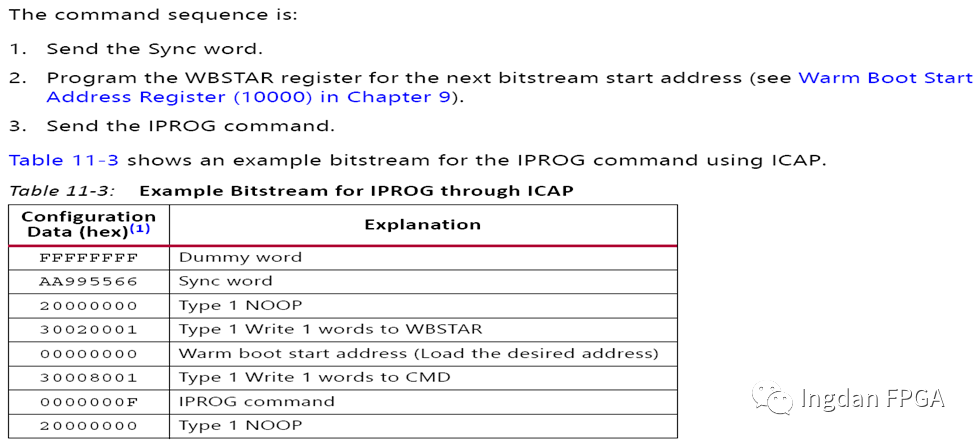

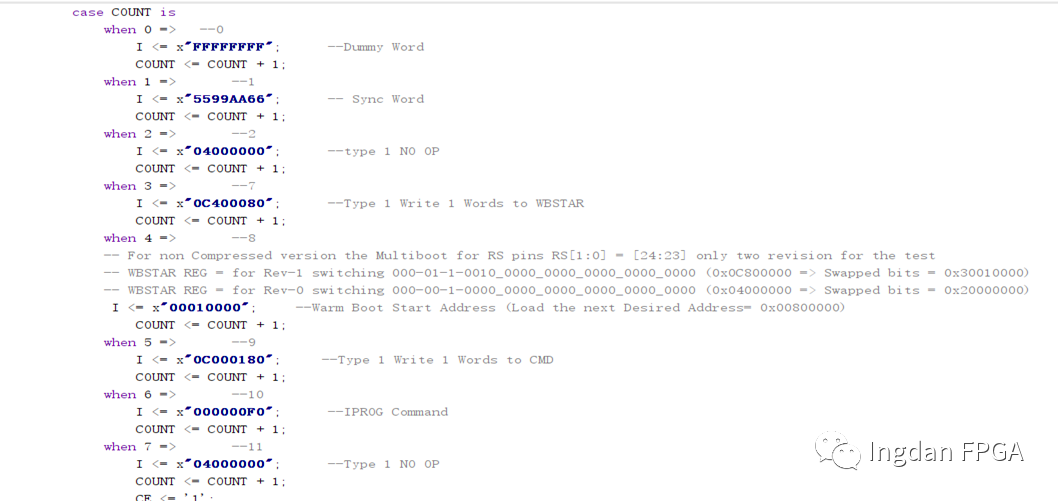

代码里面使用IPROG功能的流程如下图所示:

我们可以在点亮LED2的那个工程来做相关修改:

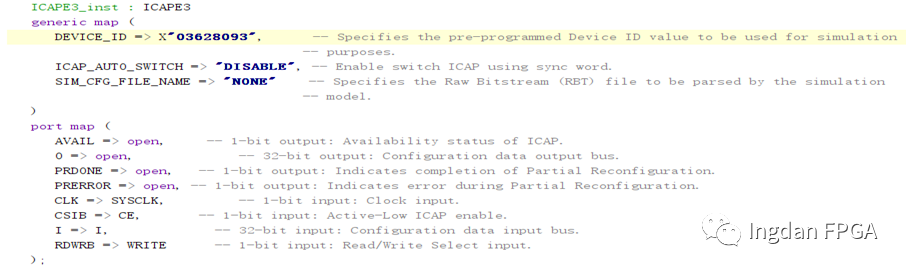

1、我们在点LED2灯的MultiBoot Image LED2工程里面加入ICAPE3代码;

2、根据前面命令流程图在代码里面实现其功能;其中Warm Boot Start Address要跟bit文件在Flash里面位置对应起来,不然跳转后会找不到对应的image导致失败。

3、建立点亮MultiBoot Image LED3工程来配合前面IPROG命令功能;这样可以通过MultiBoot Image LED2 工程里面的IPROG命令在FPGA不断电的情况下实时把切换MultiBoot Image LED3到工程来点亮LED3。

4、使用下面tcl去把两个bit文件合为一个mcs文件;

5、烧写完成后选择Boot from Configuration Memory Devive去加载FPGA,然后通过外置按键来执行MultiBoot Image LED2 工程里面的IPROG命令去实现跳转。

前面篇章对Xilinx的Multiboot进行简介和工程实现;主要参考文章有UG574\UG974\XAPP1257等等。

如果您有此类问题需要讨论或者需要实际工程验证,请联系我们: