Vivado® Design Suite 可提供围绕 IP 的设计流程,支持您将来自各种设计的 IP 模块添加到自己的设计中。此环境的核心是可扩展的 IP 目录,其中包含 AMD 赛灵思提供的即插即用 IP。IP 目录可通过添加以下内容来加以扩展:

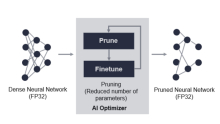

下图显示了围绕 IP 的设计流程:

在设计中使用 IP 的方法包括:

按设计进程浏览内容

硬件、IP 和平台开发

为硬件平台创建 PL IP 块、创建 PL 内核、子系统功能仿真以及评估 Vivado® 时序收敛、资源使用情况和功耗收敛。还涉及为系统集成开发硬件平台。本文档中适用于此设计进程的主题包括:

系统集成与确认

通过板级原理图和开发板布局来设计 PCB。还包含功耗、散热以及信号完整性注意事项。本文档中适用于此设计进程的主题包括:

IP 术语

Vivado IDE 使用下列术语来描述 IP、其存储位置及其表述方式。

IP 封装器

Vivado IP 封装器支持您创建即插即用型 IP,以添加到可扩展的 Vivado IP 目录。“IP Packager”Wizard(IP 封装器向导)是基于对应 IP-XACT 的 IEEE 标准(IEEE 1685 标准)《在工具流程中封装、集成和复用 IP 的标准结构》来操作的。

完成 Vivado Design Suite 用户设计汇编后,IP 封装器支持您将此设计转变为可复用的 IP 模块,以便您将其添加到 Vivado IP 目录中,并可供他人用于设计工作。您可在基于工程模式的设计或基于非工程模式的设计中使用封装的 IP。

IP integrator

Vivado® Design Suite IP integrator 工具支持您通过在设计画布上将来自 Vivado IP 目录的 IP 核与模块参考加以例化并互连,从而创建复杂的子系统设计。欲知详情,请参阅《Vivado Design Suite 用户指南:采用 IP integrator 设计 IP 子系统》(UG994)。

获取完整版《Vivado Design Suite 用户指南:采用 IP 进行设计(UG896)》 ,请扫描二维码进行下载。