随着 Zynq® UltraScale+™ MPSoC 和 Artix® UltraScale+ FPGA 取得成功,AMD 现推出两款全新器件,进一步扩展 UltraScale+ 系列。

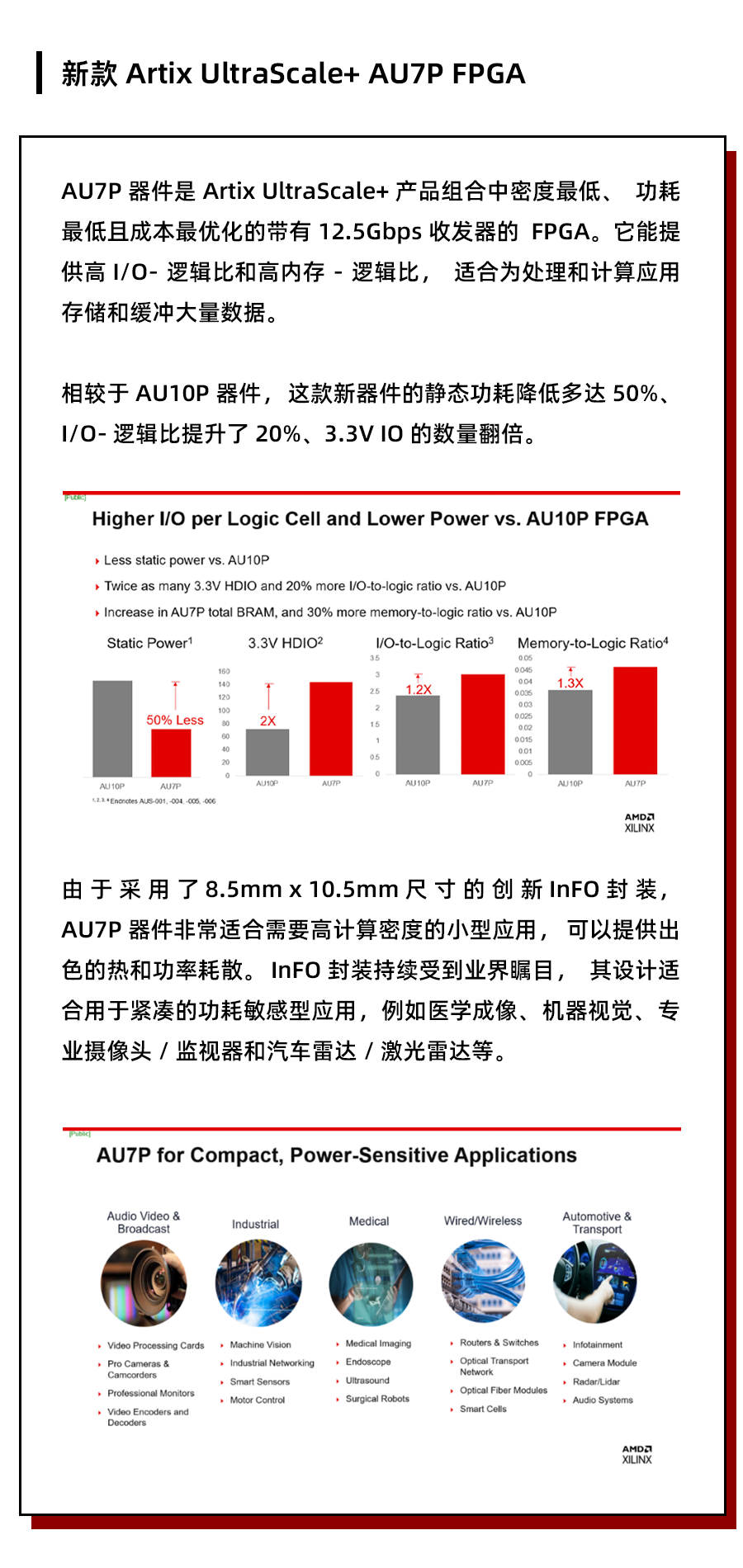

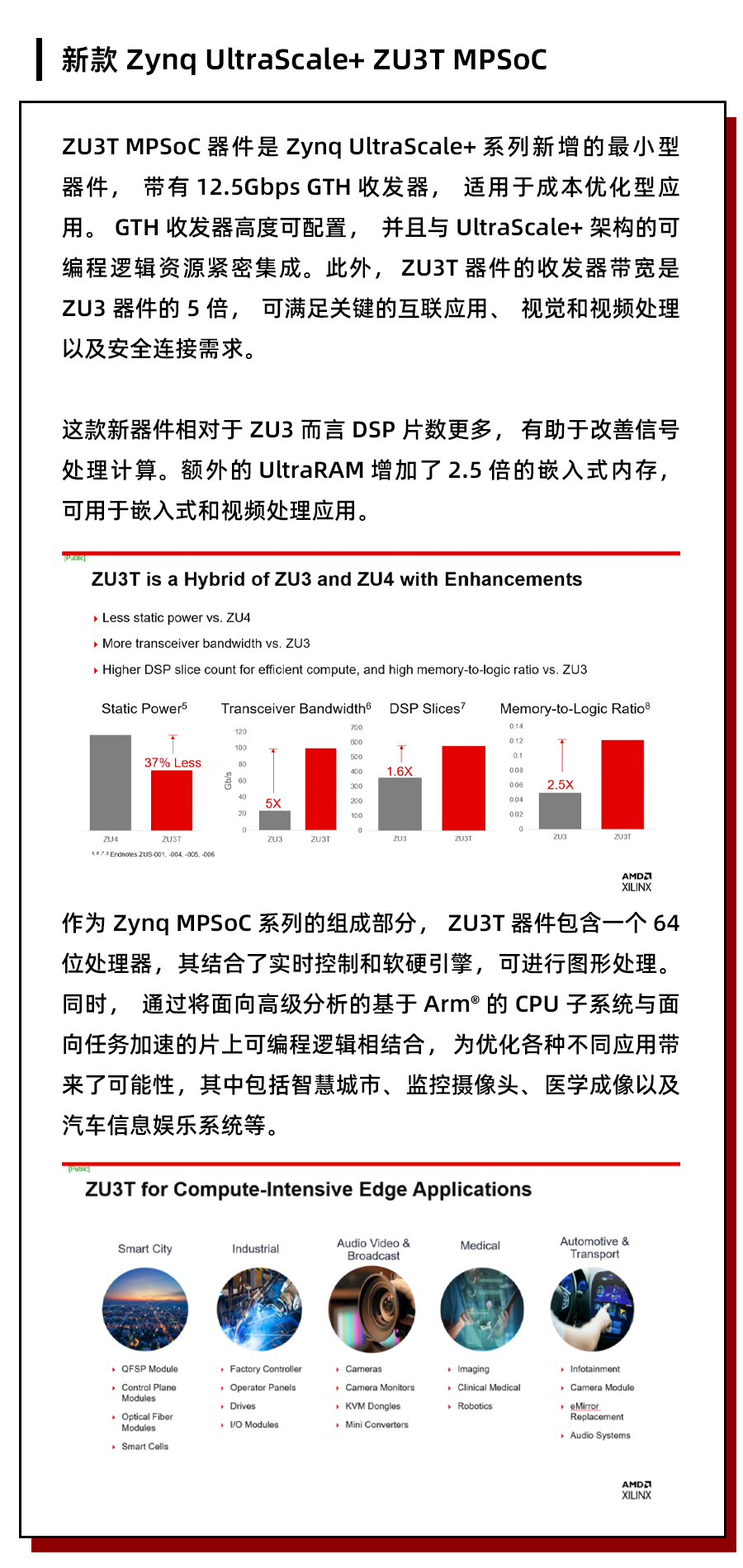

全新 AU7P 和 ZU3T 器件基于 16nm FinFET 工艺,适用于低功耗、高每瓦性能的小型应用。尽管作为具备可编程逻辑、收发器的 UltraScale+ 系列的入门款,但这些小巧、低成本、低功耗的器件提供了众多强化特性,例如高 IO-逻辑密度、UltraRAM、DSP 等。

AU7P 器件预计将于 2023 年下半年开始出货预量产和量产芯片。ZU3T 器件预计将于 2023 年上半年开始向早期试用客户提供预量产芯片,量产芯片预计将于 2023 年下半年提供。

AU7P 和 ZU3T 器件也将提供车规级( XA )器件,符合 AEC-Q100 测试规范和 ISO26262 ASIL-C 全面认证。这款可扩展的解决方案非常适合各种汽车客户平台,不仅能提供适当的每瓦性能,同时还整合了关键的功能安全和信息安全特性。

进一步了解 UltraScale+ 成本优化型 FPGA 和 SoC,请访问产品专区。

尾注:

1. AUS-001:静态功耗计算基于 AU10P 扩展,用 AU7P 在赛灵思功耗估算器 (XPE) 工具版本 2022.1.2 上的静态功耗估算,时间为 2022 年 10 月 24 日。拓展功耗参考 AU7P 逻辑单元比较差异计算得出。实际静态功耗可能与实际部件参数存在差异。

2. AUS-004:计算基于已发布的 Artix UltraScale+ 参数,使用 HDIO。AU7P 有 144 HDIO,而 AU10P 有 72 HDIO。

3. AUS-005:计算基于已发布的 Artix UltraScale+ 参数,使用总 IO (HD + HP)。AU7P 有最大 248 总 IO,而 AU10P 有最大 228 总 IO。

4. AUS-006:计算基于已发布的 Artix UltraScale+ 参数,使用总块 RAM (BRAM)。AU7P 有 3.8Mb BRAM, 而 AU10P 有 3.5Mb BRAM。

5. ZUS-001:静态功耗计算基于 ZU4 扩展,用 ZU3T 在赛灵思功耗估算器 (XPE) 工具版本 2022.1.2 上的静态功耗估算,时间为 2022 年 10 月 24 日。拓展功耗参考ZU3T逻辑单元比较差异计算得出。实际静态功耗可能与实际部件参数存在差异。

6. ZUS-004:基于已发布的 Zynq UltraScale+ 参数。ZU3 共有 24 Gb/s 带宽(4 PS-GTR @ 6Gb/s),ZU3T 共有 124 Gb/s(4 PS-GTR @ 6Gb/s + 8 GTH @ 12.5Gb/s)带宽。

7. ZUS-005:基于已发布的 Zynq UltraScale+ 参数。ZU3 有 360 个 DSP 片,而 ZU3T 有576 个 DSP 片。

8. ZUS-006:计算基于已发布的 Zynq UltraScale+ 参数,在可用情况下均使用总块 RAM (BRAM) + UltraRAM。ZU3 的总 BRAM 和 UltraRAM 为 7.6Mb,ZU3T 为 17.1Mb。