作者:Hong Han,AMD赛灵思开发者

Vivado同时支持在工程模式以及非工程模式中使用DFX流程,这里我们先从非工程模式开始介绍。

如果在下文中看到不熟悉的术语,可以参考"DFX flow I - DFX flow Introduction"。

1.分别准备顶层模块以及RM部分的综合网表

用户可以使用Vivado Synthesis或着Synplify生成综合网表

<1>顶层模块的综合网表

在做顶层模块的综合时,在顶层模块中每个RP模块都是黑盒

代码的例子(这里shift module作为RP子模块在顶层被例化)

可以看到shift module只有端口的申明,功能部分的内容是空的.

也可以使用Black_box的属性忽略RP模块中的逻辑功能,强制将其作为黑盒使用.

顶层模块的综合时会自动插入I/OBUF, 对于下层RP模块已经例化的I/OBUF的管脚(管脚在动态区的情况),需要加以下约束禁止综合器重复插入I/OBUF.

Ex:

(* io_buffer_type = "none" *) input in1;

综合可以选择直接使用synth_design命令或者为顶层模块专门建立工程导出综合网表.

综合的使用参考命令:

synth_design -flatten_hierarchy rebuilt -top <top_module_name> -part <part>

有综合工程的情况下可以打开synthesized design, 在TCL CONDSOLE中执行以下的命令导出综合网表

write_checkpoint top_synth.dcp

<2> RM 模块的综合

RM的网表用于填充在顶层模块中相应RP的黑盒. 对于同一个RP,对应的不同的各个RM的接口必须完全一致,否则组装网表时会遇到以下的报错:

[Netlist 29-77] Could not replace (cell 'XX', library 'work', file 'XX.dcp') with (cell 'XX', library 'work', file 'XX.dcp') because of a port interface mismatch; XX ports are missing on the replacing cell. XX of the missing ports are: …

因为RM是子模块,所以综合时一般不需要工具自动插入I/OBUF,因此在需要采用out_of_context 模式做综合.

在非工程模式下的synth_design的命令如下 :

synth_design -mode out_of_context -flatten_hierarchy rebuilt -top

<reconfig_module_name> -part <part>

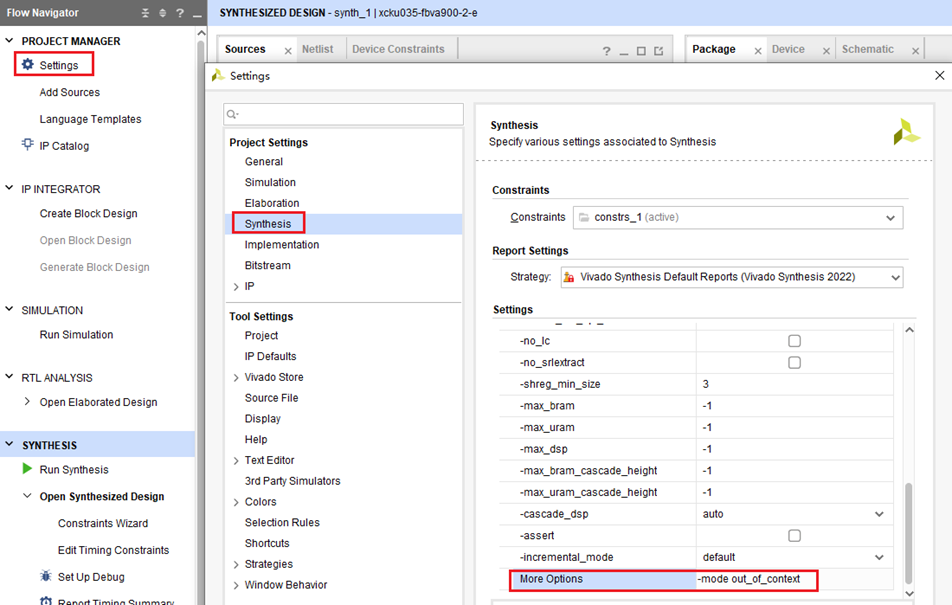

如果在综合工程中,可以在synthesis settings中加 -mode out_of_context

2.有多种方式可以组合顶层网表和RM的网表,下面会分别介绍:

<1> Add and Link Files

create_project -part <part> -in_memory

#在内存中直接创建工程,可以指定part,但是注意这依然属于非工程模式.

add_files <top>.dcp

add_files <rp1_rmA_top>.dcp

add_files <rp1_rmA_lower>.dcp

add_files <rp2_rmA_top>.dcp

#在这里分别加入了顶层的dcp,RP1的rmA顶层dcp,RP1的rmA底层dcp,以及RP2的dcp.

#在示例中,设计中有两块RP(rp1和rp2)

#<rp1_rmA_top>.dcp包含<rp1_rmA_lower>.dcp;

set_property SCOPED_TO_CELLS {<RP1_module_instance>} [get_files <rp1_rmA_top>.dcp]

set_property SCOPED_TO_CELLS {<RP1_lower_module_instance>} [get_files <rp1_rmA_lower>.dcp]

set_property SCOPED_TO_CELLS {<RP2_module_instance>} [get_files <rp2_rmA_top>.dcp]

#用文件的SCOPED_TO_CELLS属性定义这些cell的层次关系

link_design -top <top> -part <part> -reconfig_partitions

{<RP1_module_instance> <RP2_module_instance>}

#使用link_design命令组合这些网表文件, 指定在DFX设计中所包含的RP

<2>Read Netlist Design

这种方式一般用于综合网表不是Vivado生成的情况.

read_edif 可以接受多种格式的网表,包括 edf,edn和ngc(ISE XST生成的网表)

read_edif <top>.edf/edn/ngc

read_edif <rp1_a>.edf/edn/ngc

read_edif <rp2_a>.edf/edn/ngc

link_design -top <top> -part <part> -reconfig_partitions

{<RP1_module_instance> <RP2_module_instance>}

<3> Open/Read Checkpoint

open_checkpoint <top>.dcp

read_checkpoint -cell <cellname> <rp1_rmA_top> [-strict]

#打开顶层dcp网表,然后读入属于rp1的rmA的dcp网表

<4> Open Checkpoint/Update Design

这种方式用于合入顶层的RM的网表格式是edf或者edn.

open_checkpoint <top>.dcp

lock_design -level routing

update_design -cells <rp1> -from_file <rp1_b>.{edf/edn}

update_design -cells <rp2> -from_file <rp2_b>.{edf/edn}

3. 当你的RM网表中包含其他网表文件时,建议先把这些网表文件合并成一个之后再使用

合并网表的命令:

add_files [list rm.edf ip_1.edf ip_n.edf]

# Run if RM XDC exists

add_files rm.xdc

link_design -top <rm_module> -part <part>

write_checkpoint rm_new.dcp

4.DFX设计中的约束

<1> 设置HD.RECONFIGURABLE属性,定义RP模块:

set_property HD.RECONFIGURABLE TRUE [get_cells XX]

<2> 物理约束

Floorplan约束

DFX设计中RP模块强制要求有Floorplan约束(Pblock),动态区的逻辑只能放在RP的Pblock中.

管脚约束

Partition Pin约束

可以将Partition Pin放在特定位置或者区域内

set_property HD.PARTPIN_LOCS INT_R_X4Y153 [get_pins <hier/pin>]

set_property HD.PARTPIN_RANGE SLICE_X4Y153:SLICE_X5Y157 [get_pins

<hier/pins>]

<3> 时序约束

5.Implementation的相关命令

<1>参考以下Configuration1(又称为Initial Configuration)的命令实例

open_checkpoint top_synth.dcp

read_xdc top_impl.xdc

set_property HD.RECONFIGURABLE true [get_cells rp1]

read_checkpoint -cell rp1 rp1_a_synth.dcp

#以上命令是组合顶层网表和RM的网表,在前文中已经介绍过

opt_design

place_design

route_design

#以上命令和普通流程的implement一样,可以根据需要加入phys_opt_design步骤或者修改各阶段命令的directive

write_checkpoint config1_routed.dcp

#生成Configuration1布局布线后完整设计(静态+动态逻辑)的dcp(Top routed dcp)

write_checkpoint -cell rp1 rp1_a_route_design.dcp

#生成动态逻辑的布局布线后dcp(RM routed dcp)

update_design -cell rp1 -black_box

#去掉动态逻辑(为了加入新的动态逻辑网表做准备)

lock_design -level routing

#锁定所有静态部分的布局布线信息, 保证静态部分在之后所有的Configuration中都不再有任何变化

write_checkpoint static_routed.dcp

#生成只包含静态逻辑的dcp(此时动态模块为黑盒)

<2>参考以下Configuration2的命令实例

open_checkpoint static_routed.dcp

read_checkpoint -cell rp1 rp1_b_synth.dcp

opt_design

place_design

route_design

write_checkpoint config2_routed.dcp

write_checkpoint -cell rp1 rp1_b_route_design.dcp

6.验证所有Configuration的静态逻辑以及边界一致

这里我们使用pr_verify命令

验证Configuration1和Configuration2 布线后设计的命令

pr_verify -full_check config1_routed.dcp config2_routed.dcp -file pr_verify_c1_c2.log

验证多个布线后设计的命令:

pr_verify -full_check -initial config1.dcp -additional {config2.dcp config3.dcp} -file three_config.log

7.生成比特流文件

<1> 默认生成完整设计的bit文件与Partial bit文件

open_checkpoint config1_routed.dcp

write_bitstream config1

<2> 只生成Partial bit文件而不生成完整设计的bit文件

write_bitstream -cell rp1 RM_count_down_partial.bit