作者:Stefano Lovati, 来源:EE Times欧洲版

FPGA日益广泛的使用正使设备面临可能的攻击,从而就突出了安全问题——知识产权保护和敏感数据保护。本文分析了FPGA可能暴露的主要漏洞,并介绍了可编程器件制造商所采用的作为防篡改措施的技术。

可编程数字器件的大规模引入,使得嵌入式系统的实现具有越来越多的高级功能。现场可编程门阵列(FPGA)已经实现了曾经只能通过专用硬件设计才能实现的性能。然而,与定制硬件系统相比,FPGA具有高灵活性和高可配置性等优点,可以满足广泛的应用需求。将一个或多个内核处理器与FPGA模块集成在一起的SoC的问世,证实了逐步采用高度集成的可编程器件的趋势,一个例子是Xilinx的Zynq(图1)。

图1:Xilinx Zynq UltraScale+。(图片来源:AMD Xilinx)

FPGA日益广泛的使用正使设备面临可能的攻击,从而就突出了安全问题——知识产权保护和敏感数据保护。获取到FPGA内容的恶意行为者将可能获得专有信息和算法,并有可能对公司造成经济和形象损失。此外,FPGA配置可能会因非法或欺诈目的而受到更改。

下面,我们分析了FPGA可能暴露的主要漏洞,并介绍了可编程器件制造商所采用的作为防篡改措施的技术。

漏洞类型

有多种方式可以破坏FPGA的安全性和数据完整性,包括:

逆向工程。该技术最初在第一批ASIC和IC上使用,是通过对器件进行破坏性分析,对所获得的层运行后续扫描,来跟踪内部版图和互连的。然而,在FPGA的情况下,分析却是非破坏性的,它旨在拦截配置比特流并对其进行解码,后者通常驻留在闪存中,并在启动期间被传输到FPGA的SRAM。即使配置比特流未以明文形式传输,它也可能暴露于使用自动分析工具从外部执行的攻击。由于比特流包含重建FPGA配置所需的所有信息,因此必须以所有可能的方式对其内容进行保护。

侧信道攻击(SCA)。这涉及对输入/输出信号的组合进行监视和采集,检测器件温度以突出显示最热的芯片区域(电流穿过的区域),并测量运行期间的功耗和电磁辐射,直至检查单个存储单元或晶体管。由此获得的信息可用于破坏器件的安全性或利用它进行其他类型的攻击。SCA使用统计模型,例如差分分析和相关分析,对FPGA运行期间所监测的物理量进行执行。例如,电流消耗揭示了密码算法迭代执行期间的峰值,而这些峰值取决于所处理的数据和所执行的指令。然后,适当的数学模型可找到吸收变化与所执行硬件操作之间的相关性,从而揭示解码密钥的价值。

热激光刺激(TLS)。该技术常用于故障分析,但也可用于定位和读取芯片内存的内容,目的是窃取比特流解码密钥等秘密信息。这种攻击技术尚未证明适用于配备了SCA反制措施的现代集成电路。TLS攻击需要很长的执行时间(大约几个小时)和昂贵的设备(此类攻击必须使用专业显微镜来进行故障分析,其成本高达100万美元)。但是由于即使器件未通电也可以进行攻击,因此可编程逻辑器件制造商不能忽视此类攻击。

比特流改变。通过在从外部PROM到片上SRAM的传输过程中修改比特流内容,这可能会影响FPGA的行为。

回读攻击。许多FPGA支持通过JTAG编程和调试接口重新读取比特流的内容。虽然有内置机制可以防止这种攻击,但始终可以选择绕过安全措施。

安全措施

随着时间的推移,FPGA制造商推出了旨在防止或阻止这些攻击的对策,同时保护可编程器件的安全性。

第一种普遍采用的技术是针对比特流加密,然后通过集成在芯片中的适当功能块在硬件级别执行其解码。最广泛使用的加密标准之一是高级加密标准(AES)。AES基于Rijndael算法,使用128、192和256位的对称密钥(使用相同的密钥进行加密和解密)。在编程阶段,算法将生成密钥并将其存储在FPGA的电池备份RAM (BBRAM)内,这是一种随机存取存储器,其内容由缓冲电池保存(其持续时间可达几十年)。在引导阶段,集成的AES引擎将接收比特流,对其进行解密,并将配置数据传递给配置逻辑。因为配置数据在任何I/O端口上都不是明文可见的,所以不可能从外部拦截比特流。

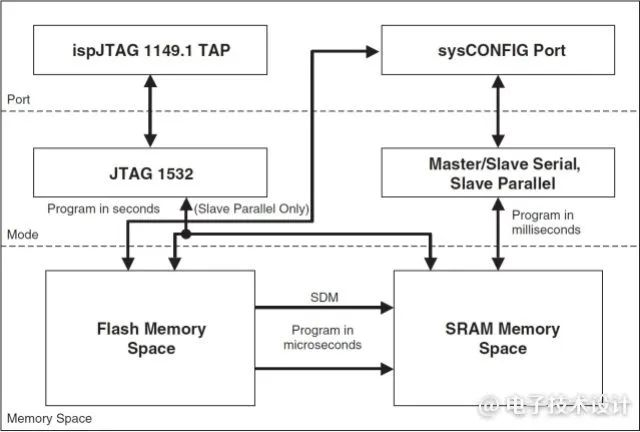

比特流加密的另一种技术是将FPGA配置存储在芯片内部,仅使用内部通信总线在启动时加载它。图2显示了Lattice XP FPGA的编程框图。配置比特流可以从内部闪存加载到SRAM,此操作不仅更安全,而且速度更快,只需几微秒。也可以通过JTAG1532接口(也用于对闪存进行编程)从外部加载比特流,尽管此操作需要更长的时间才能完成(几秒钟)。

图2:LatticeXP编程框图。(图片来源:Lattice Semiconductor)

在一些FPGA型号上,解码密钥还可以在编程阶段存储在一次性可编程存储器中,从而增加对外部攻击的保护程度。

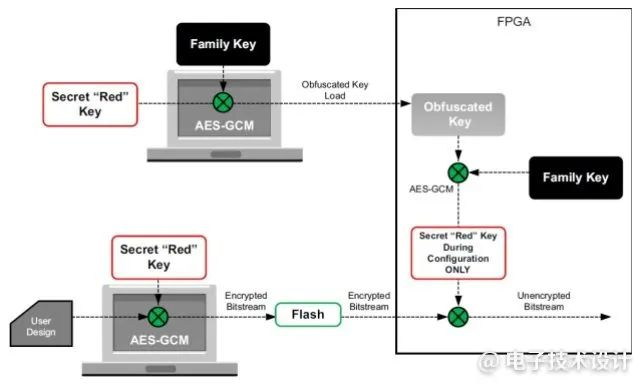

Xilinx在UltraScale系列上采用的密钥混淆技术是另一种安全措施。如图3所示,该方法使用AES-GCM算法,通过将家族密钥(仅Xilinx已知)与用户所选择的密钥相结合来获得混淆密钥。这样获得的密钥将存储在FPGA中。比特流将使用AES-GCM和用户密钥加密并存储在外部闪存中。对于启动期间的比特流解密,将应用相反的过程:将混淆密钥和家族密钥组合以获得所需的用户密钥。

图3:混淆密钥机制。(图片来源:AMD Xilinx)

为了应对旨在注入不正确比特流的攻击,许多FPGA实施了拒绝加载利用不正确密钥编码的比特流并在该配置校验和不正确时将其擦除的机制。

为了增强对SCA的保护,许多FPGA会监控并计算任何错误比特流解码的发生次数。一旦达到某个可编程阈值,就会将存储的密钥擦除,并必须对器件进行重新编程。

虽然FPGA似乎极易受到捕获密钥和解码比特流的攻击,但这类器件的制造商已采取足够的措施让用户能够实施有效的对策。当今市场上可用的不同类型的FPGA,提供了与任何类型的应用兼容的必要安全级别。

参考原文:Security and Anti-Tamper Challenges of Programmable Devices,由Franklin Zhao编译。