作者:Samk,AMD赛灵思工程师

UHD-SDI RX Subsystem IP 核与 UHD-SDI TX Subsystem IP 核在编写设计时具有多个设计示例可用,但所有这些设计示例均为直通设计的变体。如需了解有关这些设计的信息,请参阅 (PG289) 和 (PG290)。

本篇博文将侧重于概述如何以 ZCU106 开发板为目标,创建和运行仅限 TX 的设计。

注:此设计按现状提供,不含任何保证。它是在正常发布/测试流程外构建的,仅用于提供指示信息。

SR 门户不支持本设计。如果您对本设计有疑问,请在赛灵思视频论坛板块上发帖。

本设计演示了如何在 ZCU106 Rev 1.0 开发板上使用 Vivado 2019.2 工具集来构建和运行 SDI TX 系统。

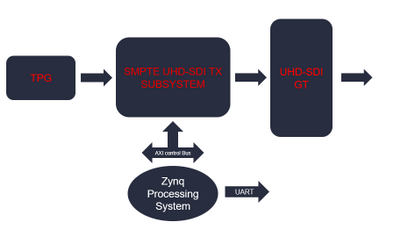

本设计是基于产品指南中发布的直通设计创建的,随后经过更新以适用于仅限 TX 的设计。其目的是为了演示如何在仅限 TX 模式下快速实现 UHD-SDI TX 子系统和 UHD-SDI GT。

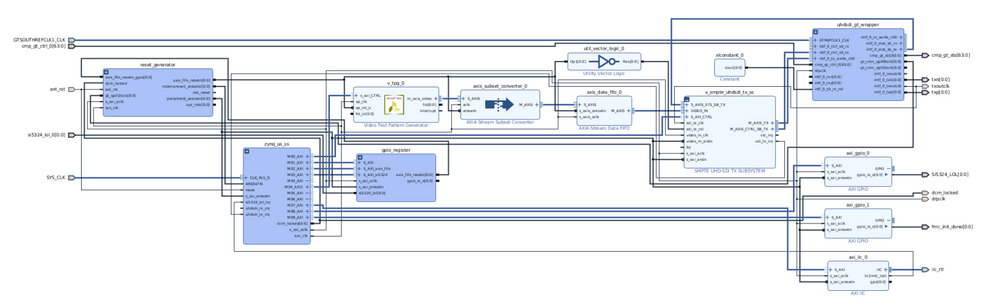

它包括下列组成部分:

复位功能

Zynq 子系统例化,用于控制 IP。

GPIO 用于监控状态(来自原直通设计且保留不变)

TPG 用于创建视频数据

子集转换器,用于将 TPG 从 8 BPC 转换为 10 BPC

FIFO(来自原直通设计)

UHD-SDI TX 子系统

UHD-SDI GT

已使用 Onmitek4K Ultra 对其进行了功能测试。

使用提供的脚本创建比特流

1. 在命令行或 Vivado 终端内,运行来自以下目录的 Tcl 脚本:

Vivado -source v_smpte_uhdsdi_rx_ss_0_ex.tcl

2. 等待脚本完成,然后运行 Vivado 生成比特流。

此操作能以脚本模式完成,也可以打开 Vivado GUI 并遵循典型的综合、实现、比特流生成流程来完成。

3. 生成比特流后,导出 XSA 文件。

如何基于 XSA 来创建 ELF 文件:

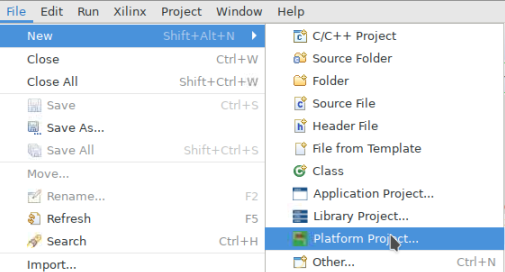

1. 打开 Vitis GUI。

2. 创建新的平台工程并指向从 Vivado 工程导出的 XSA。

3. 使用构建工具来构建 BSP。

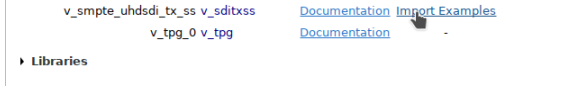

4. 构建好 BSP 后,选择“Drivers”(驱动程序)中的“Import Examples”(导入示例)。

5. 导入 xsdi_example

6. 将 /src 文件 xsdb_* 替换为 /SW 内的文件。

这些文件已经过编辑,适用于仅限 TX 的硬件设计。

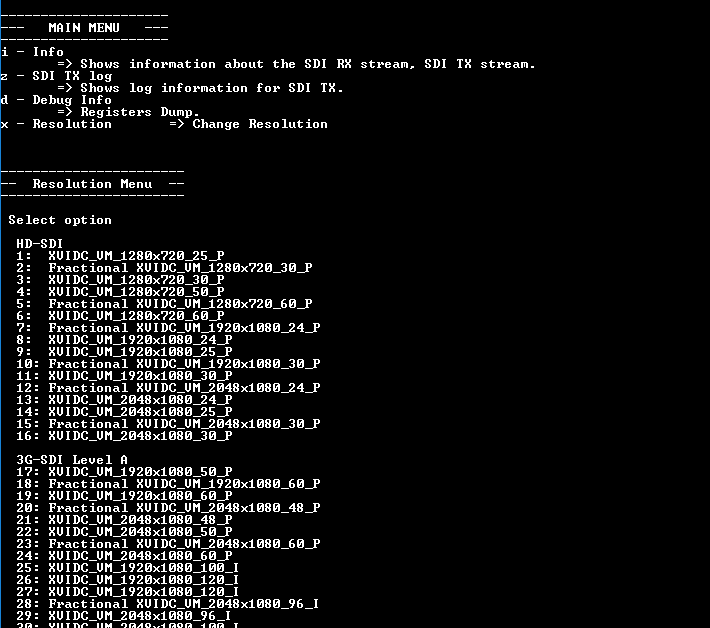

7. 构建并测试。下图显示了 UART 控制台。

注:如需了解有关构建和测试的更多信息,请参阅 (PG289) 和 (PG290) 内记述的默认设计示例。