作者:Han Hong,AMD赛灵思工程师

在一些大型项目的设计中,可能会涉及多个公司或者同一公司多个部门之间的协作,在最终归并完整设计时,你需要提交你负责的子模块的设计,可以以RTL源文件形式提交. 当你希望对你的RTL源文件进行加密,可以在Vivado中采用 IEEE-1735-2014 version 2 (V2)的标准, 对RTL源文件进行加密,允许对方将你的加密RTL源文件应用到Vivado中进行综合,仿真或者实现. 在这里我们会解释一下在使用源文件加密时的一些基本概念以及一些常见的问题。

许可证(License):

使用IEEE-1735-2014 version 2标准加密需要获得AMD-Xilinx授权的许可证。获取免费许可证的详细流程可以参考AR-68071.

建议使用公司邮箱发送邮件,文本使用英语,并告知你使用的Vivado版本.

68071 - Vivado - How do I enable IEEE-1735 Version 2 encryption in Vivado? (xilinx.com)

公开的密钥(Key)

在Vivado的安装目录下可以找到公开的密钥:

<Install_Dir>/Vivado/<version>/data/pubkey/

加密命令 encrypt:

加密使用的Vivado中的encrypt命令,可以在GUI下执行,也可以在命令行下执行

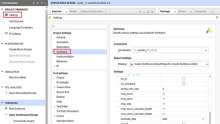

GUI下执行encrypt命令:

1.打开Vivado界面

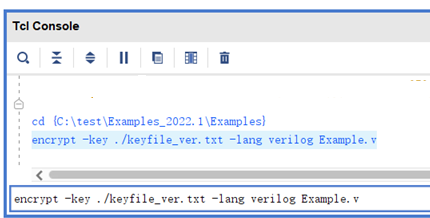

2.在TCL CONSOLE中cd 到目标路径

3.在TCL CONSOLE中键入encrypt命令,按回车执行

在命令行下执行encrypt命令:

1. 打开命令行界面,设置Vivado环境

C:\Xilinx\Vivado\2022.1\settings64.bat

2. cd 到目标路径

cd C:\test\Examples_2022.1\Examples

3. 启动Vivado TCL模式

vivado -mode tcl

4. 在Vivado的提示符下执行encrypt命令

vivado% encrypt -key ./keyfile_ver.txt -lang verilog Example.v

- key 选项用来指定加密文件,如果密钥嵌在源文件中,可以不使用-key选项.

- lang 选项用来指定加密文件的类型,systemverilog和Verilog 都选择verilog即可(vhdl | verilog )

如果不希望原来的源文件被生成的加密文件覆盖,可以使用-ext选项,指定新生成的加密文件的后缀,这样原来的源文件在加密后会依然保留:

Ex:encrypt -key ./keyfile_ver.txt -lang verilog Example.v -ext .vp

在原目录下的文件: Example.v -> Example.v + Example.vp

如何理解密钥文件的内容

以下是一个实际的Key文件

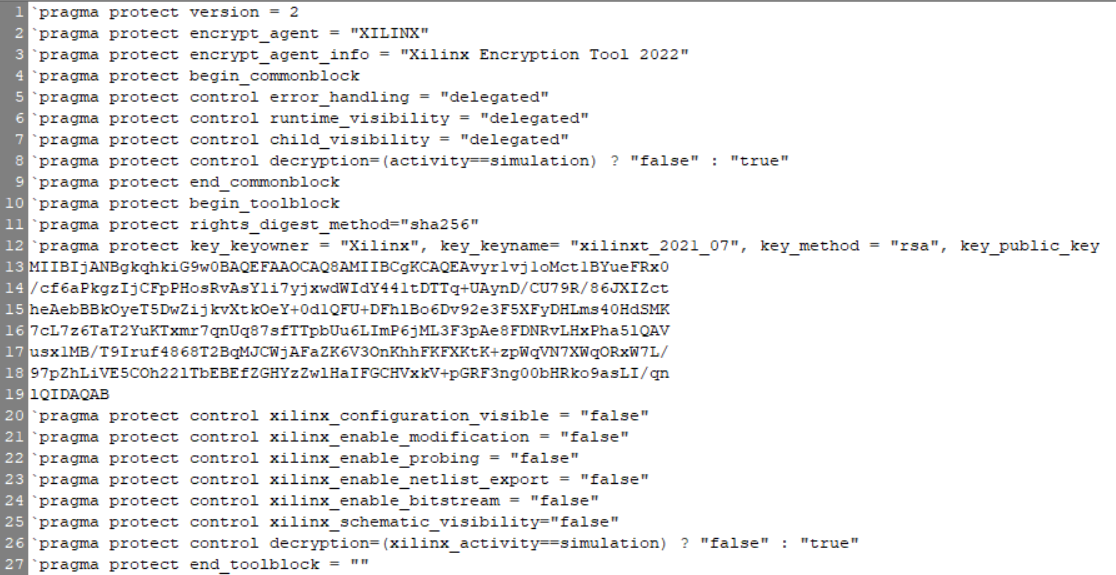

`pragma protect version = 2

`pragma protect version = 2

#用的是IEEE-1735-2014 V2

`pragma protect encrypt_agent = "XILINX"

`pragma protect encrypt_agent_info = "Xilinx Encryption Tool 2022"

#加入一些关于Key自身的识别信息

`pragma protect begin_commonblock

…

`pragma protect begin_commonblock

#其中包含的内容是常规权力定义

‘protect begin_toolblock

...

‘protect end_toolblock=””

#其中包含的内容是工具特有的权力定义

密钥部分可以直接替换成安装目录下的公钥

以下是几个Xilinx-AMD定义的,特有的权力定义

xilinx_configuration_visible

是否显示综合之后的网表中LUT的配置信息

拒绝的话,只能看到LUT的连接,这些LUT的功能是什么无法看到.

xilinx_enable_modification

是否允许使用 Vivado 工具修改受保护区域内的网表信息(层次结构、连接、LUT 等)

xilinx_enable_probing

是否允许客户在受保护区域中插入或实例化Vivado 探针工具

xilinx_enable_netlist_export

Vivado是否允许导出受保护区域的网表

xilinx_enable_bitstream

是否允许Vivado 工具导出比特流文件

xilinx_schematic_visibility

Vivado是否允许在原理图或层次结构查看器中显示受保护区域的模块名称

选择不可见的话,受保护的cell在原理图和时序报告中统一显示为<hidden_cell>

有条件的权力定义

`protect control <right> = <condition> ? <true_expression> : <false_expression>

让加密的文件只在特定的步骤中可以被工具解密读取.

Ex: `protect control decryption = (xilinx_activity==simulation) ? "false" : "true"

代表在Vivado仿真时,条件为true,总的结果是false,所以相关文件只能综合实现,无法用于仿真.

直接把密钥嵌入到RTL源文件中

允许客户直接把密钥的内容直接贴到RTL源文件中protect begin和protect end之间的内容就是用户原始RTL里的内容.

之前提过嵌入密钥内容后,不再需要-key的选项.

`pragma protect begin

User RTL content

`pragma protect end