来源:内容由半导体行业观察(ID:icbank)编译自servethehome

在 ISSCC 2023 上,AMD首席执行官 Lisa Su 博士讨论了堆叠组件以及为什么需要先进的封装来实现未来的 Zettascale 计算。部分讨论围绕内存展开。

AMD 在 ISSCC 2023 上谈论堆叠计算和 DRAM

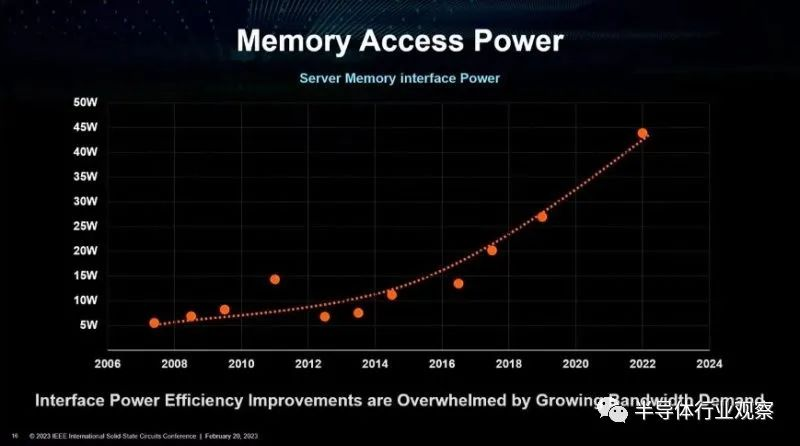

构建更大系统的一大限制因素是内存访问能力。这有两种形式,主要来自高速接口以及简单地向服务器添加更多内存通道。这是 AMD 从 2007 年左右到 2023 年的图表。

内存访问能力

我们最近讨论了过去十年中英特尔至强和 AMD EPYC 每核心和每插槽内存带宽的增加,并做了一个DDR5 服务器 RDIMM 文章,其中我们展示了为什么从 8 通道 DDR4 到 12 通道 DDR5 的跃升如此重要性能大跃进。

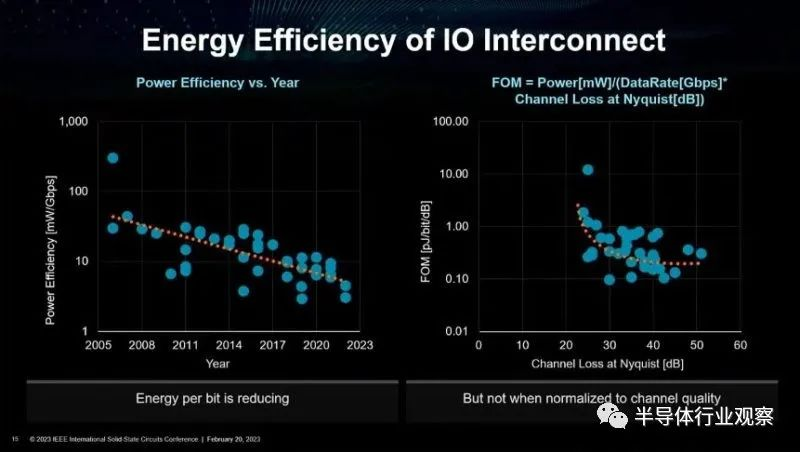

最大的挑战之一是在 I/O 端,那里的电源效率越来越好,但通道损耗正成为一个更大的挑战。

IO 互连的能源效率

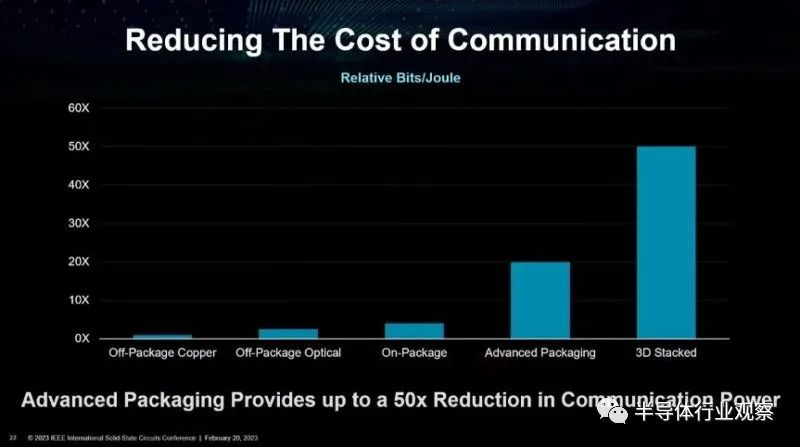

这样做的最终影响是,从能源角度来看,封装到 DRAM 的成本越来越高。我们已经看到 HBM 已集成在 CPU 和 GPU 封装上的案例,但还有其他技术。其中包括使用共同封装的光学器件和 3D 芯片堆叠。

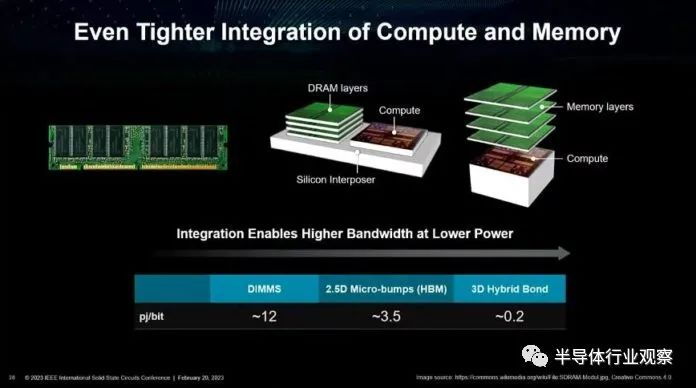

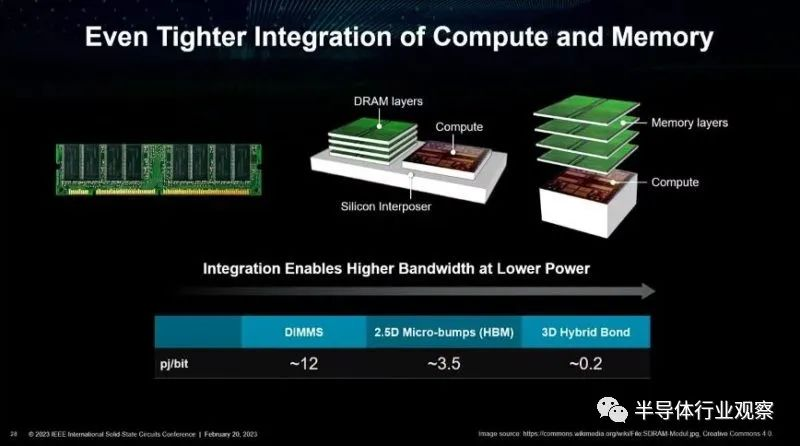

在 ISSCC 2023 上,AMD 展示了通过使用硅中介层(类似于 GPU 现在集成 HBM 的方式)使内存更接近计算的概念,以及在计算上堆叠内存的未来。通过 3D 堆栈移动数据比尝试将信号驱动到 DDR5 DIMM 插槽消耗的功率少得多。

更紧密的计算和内存集成

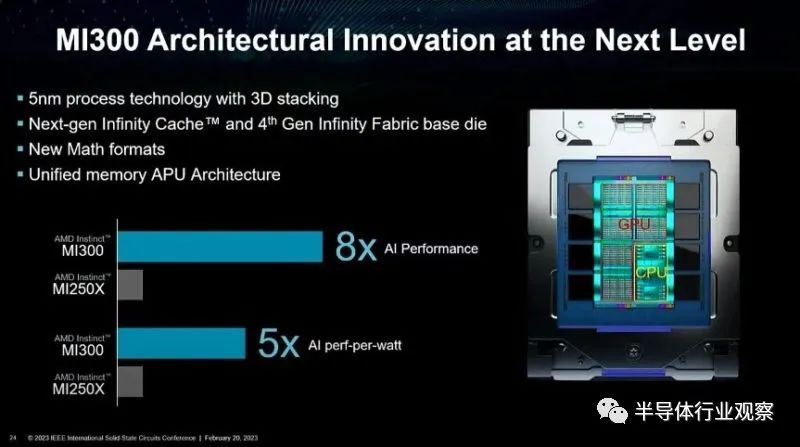

在谈话中,讨论了即将推出的 AMD Instinct MI300。本次演示中有趣的部分之一是 MI300 中 CPU 和 GPU 内核下方的 Infinity Cache 和 Infinity Fabric 芯片的 3D 堆叠。

AMD Instinct MI300

作为参考,我们在当前的Milan-X和即将推出的Ryzen 7000X3D系列中看到的 3D SRAM 堆叠将 SRAM 放置在 CPU 芯片上方。MI300 将改变这一点并将缓存置于 CPU 芯片下方。冷却是一项重大挑战,因此让热计算块更靠近液体冷却块是有意义的。

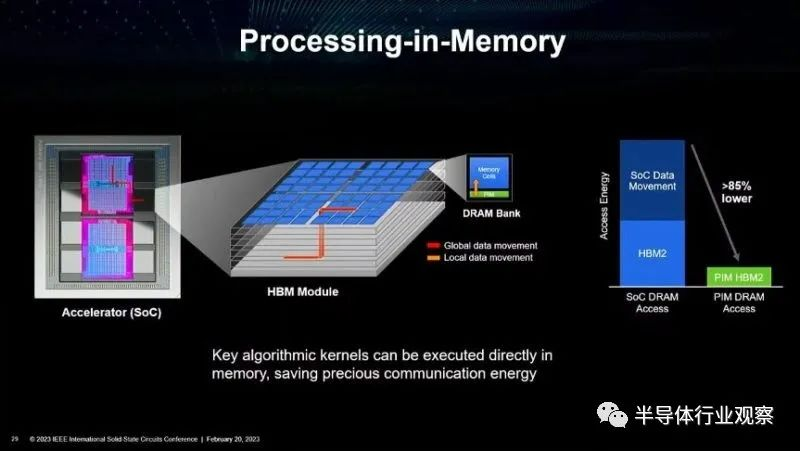

谈话中讨论的另一个快速话题是内存处理。我们在 Hot Chips 33 上介绍了三星 HBM2-PIM 和 Aquabolt-XL, AMD 表示正在与三星合作研究内存计算。这里的想法更加引人注目,因为不必将数据从内存中移出即可对其进行一些计算。

内存处理

这似乎比内存的一些封装改进还差得远。

最后的话

在系统内和机架内移动数据正成为业界关注的焦点。数据移动的能量和性能成本会降低系统的整体效率。因此,整个行业都在努力超越带有附加 DRAM 模型的典型 CPU,并转向新的架构。