作者:Simon Yang ,来源:Comtech FPGA微信公众号

一. AMD FPGA的加载模式简介

在不带内置ARM核的AMD FPGA产品系列中,FPGA的程序加载方式并没有发生大的变化,仍旧采用JTAG、Master SPI、Serial Configuration、Master BPI、Select MAP几种加载模式,关于每种加载模式的电路图和工作原理不再进行描述,每个产品系列的configuration guide中都有详细描述,关于这部分的硬件设计和工作原理,用户可以参考对应的文档如UG470、UG570等。

在不同系列的pure FPGA产品发展过程中,加载模式发生了一些细微变化简述如下:

A. 自7系列产品开始Master SPI加载模式增加了x2、x4模式,自Ultrascale系列开始在x2、x4的基础上又增加了x8模式(dual quad SPI模式);

B. 自7系列产品开始不再支持AMD自有的FLASH PROM产品,也不再更新自有的FLASH PROM产品,在UG908文档中不断更新测试过的第三方FLASH,如Micron、Spansion、ISSI等厂商的SPI FLASH和BPI FLASH;

带内置ARM核的SOC产品中,芯片内部集成了bootrom并且需要使用FirstBootloader来进行加载,因此其加载模式和加载流程与pure FPGA器件有区别,常见的boot mode包括JTAG模式、QSPI模式、SD Card模式、EMMC模式、NAND模式、USB模式等,详细描述可以参考UG585和UG1085文档中的boot and configuration章节,SOC系列产品的加载方式我们将在以后文章中单独说明。

本文的写作初衷是介绍Select MAP加载模式,因此后面的描述基本都是基于不带内置ARM核的FPGA来展开。

二. bit、bin和mcs文件的区别

在使用JTAG或者其他芯片来Program FPGA和FLASH时,我们最常用到的三个文件是bitstream文件、bin文件和mcs文件,最常遇到的问题是这三个文件有什么区别,在这一章节中我们不展开对文件内部详细数据格式的解析,主要针对这三个文件的主要差别和使用场景进行对比和描述。

在configuration userguide中,有如下描述:

bit、bin和mcs文件

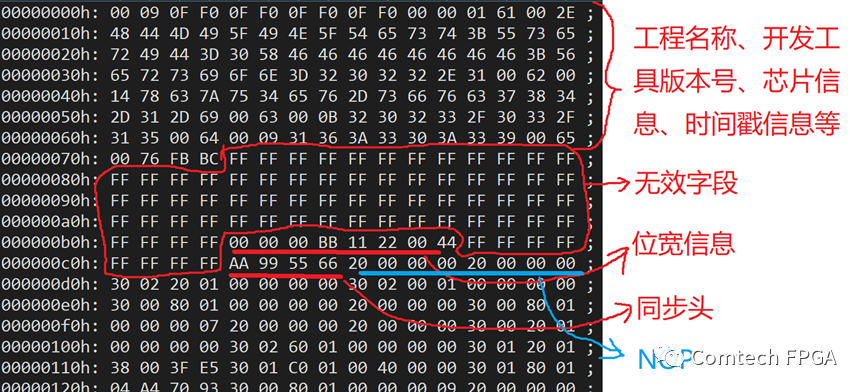

我截取一个真实bitstream文件的开始部分,如下图:

bit文件前端内容

我们在JTAG Program FPGA的时候,使用的是bitstream文件;在Serial模式、SPIx1模式Program FLASH的时候,bin文件和mcs文件都可以使用;在SPIx4模式、SPIx8模式、BPI模式、SelectMAP模式Program FLASH的时候,使用的是MCS文件;在SelectMAP模式使用外部其他芯片(如MCU、ARM、CPU、CPLD、FPGA)Program FPGA的时候,使用的是bin文件,但是需要我们自己做bit swap。

从上面两图展开介绍:bitstream文件开头部分包含工程名称、开发工具版本号、芯片型号、时间戳、加载位宽、同步头等信息,真正被Program进入FPGA的有效bit在同步头和紧跟着的NOP之后;在bin文件没有做bit swap的时候,bin文件直接从全FFFF的无效字段开始,比bitstream文件少了工程名称、开发工具版本号、芯片型号、时间戳、加载位宽、同步头等信息;而mcs文件通常比bitstream文件、bin文件大很多,是因为mcs文件中加入了对FLASH的操作命令以及其他一些信息,并且在多位数据位宽时,mcs文件中的有效数据部分根据加载位宽做了bit swap。

三. SelectMAP加载模式的优缺点

什么会有场景需要使用SelectMAP加载模式?SelectMAP加载模式有哪些优缺点呢?SelectMAP模式有如下特点:

A. 可以外供时钟给CCLK,频率确定;而Serial模式和Master SPI模式下FPGA自己震荡产生的CCLK频率低、频率不精确;----优点

B. SelectMAP模式可以支持8bit、16bit、32bit加载;----优点

C. 在板卡上有多个FPGA芯片、MCU+FPGA、ARM+FPGA等架构下,可以共用一个FLASH、SD卡、EMMC等存储介质来存储加载文件;----优点

D. 占用的IO数量多;----缺点

E. 需要外面一颗芯片来实现SelectMAP模式的加载;----缺点

综合以上特点,SelectMAP模式在两种应用场景中会有优势:

场景一:在使用Serial模式和Master SPI模式的时候,加载数据线位宽只能是1、2、4或8,在Master Serial和Master SPI模式下CCLK时钟由FPGA内部震荡产生,这个时钟频率是不准确的,而且我们在产生bitstream的配置选项中选择的configuration rate频率有限;所以在期望缩短加载时间的应用场景下,更高位宽更高CCLK频率的SelectMAP模式可以大大缩短加载时间。

场景二:在板卡上有多个芯片时,可以共用加载文件的存储介质,来减少存储介质芯片数量。

四. SelectMAP加载的硬件和软件设计

SelectMAP硬件设计:

在configuration userguide中给出了SelectMAP模式的硬件原理图示例:

单片FPGA的SelectMAP加载

多片FPGA的SelectMAP加载

Select MAP模式软件设计:

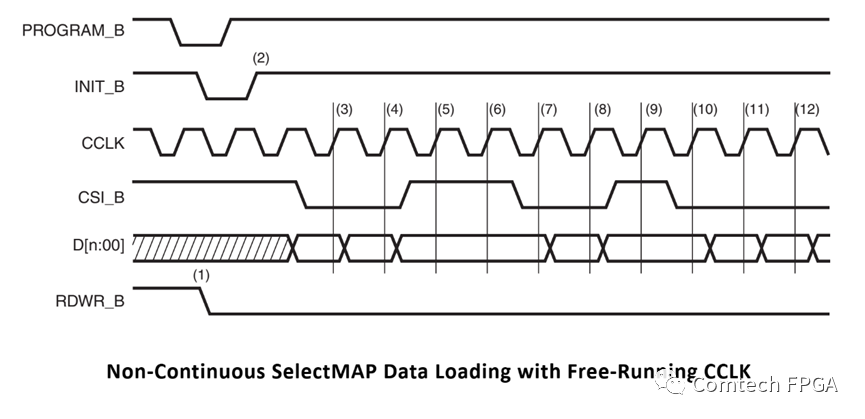

而FPGA前端负责实现Select MAP加载的主控器件,可以是MCU、CPLD、ARM、FPGA等,只需要按照如下时序将bin文件中的有效内容做bit swap后写入到FPGA即可。

以8bit SelectMAP模式为例:

连续数据loading SelectMAP模式

不连续数据loading SelectMAP模式

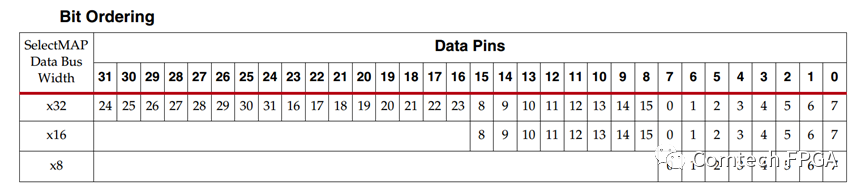

需要说明的是在SelectMAP模式中的bit swap,需要根据数据线位宽在主控器件中实现如下bit swap:

SelectMAP模式bit swap

如果前端主控器件是MCU、ARM、CPU,可以参考AMD官方参考设计XAPP583,C代码在XAPP583中可以获得;如果前端主控器件是CPLD或者FPGA,作者曾经写Verilog代码实现过一片小FPGA做主控、通过Select MAP模式加载多片FPGA,欢迎咨询作者本人。

如果您在FPGA加载方面有疑问需要讨论,欢迎联系:

simonyang@comtech.cn

charlesxu@comtech.cn