开发者分享 | 从已布线设计中提取模块用于评估时序收敛就绪状态

judy 在 周四, 05/20/2021 - 16:56 提交

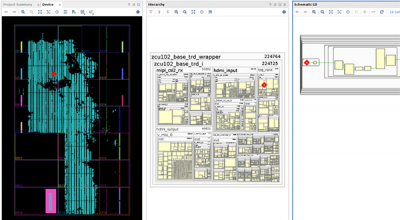

本文旨在提供一种方法,以帮助设计师判断给定模块是否能够在空裸片上达成时序收敛。 如果目标模块无法在空裸片上达成非关联 (OOC) 时序收敛,则恐难以与设计其余部分达成关联性时序收敛。设计师可从完整设计中提取目标模块、对其进行布局规划、约束,然后通过实现工具来运行这些模块,以判断是否能够独立达成时序收敛。

本文旨在提供一种方法,以帮助设计师判断给定模块是否能够在空裸片上达成时序收敛。 如果目标模块无法在空裸片上达成非关联 (OOC) 时序收敛,则恐难以与设计其余部分达成关联性时序收敛。设计师可从完整设计中提取目标模块、对其进行布局规划、约束,然后通过实现工具来运行这些模块,以判断是否能够独立达成时序收敛。

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

本文档旨在描述推荐的设计方法,帮助用户在 Vivado® Design Suite 中有效利用赛灵思 FPGA 器件资源,并加速完成设计实现和时序收敛。提供推荐方法背后的原理,以支持用户制定出明智的设计决策。

本文描述了用于实现赛灵思 FPGA 器件资源的有效利用以及在 Vivado® Design Suite 中加速设计实现和时序收敛的推荐设计方法论。提供推荐方法背后的原理,以支持用户制定出明智的设计决策。

本文整理自Xilinx公开课:Vivado时序收敛技术。有些知识在公开课中讲的并不是很细,因此我又对其进行了整理,分为了几篇文章。

通过之前的博文,我们已经学会了如何使用 Report QoR Assessment (RQA) 和 Report QoR Suggestions (RQS) 来改进总体设计分析以及设计的时序收敛体验。本篇博文将通过一个具体设计示例来演示如何在实现流程中将 RQA 与 RQS 结合使用。

本次系列研讨会将由赛灵思战略应用高级工程师 Lauren Gao(高亚军)带领大家从基础到进阶,一站式领略 Vivado 这款神奇的开发工具。

FPGA毕竟不是ASIC,对时序收敛的要求更加严格,本文主要介绍本人在工程中学习到的各种时序约束技巧。

首先强烈推荐阅读官方文档UG903和UG949,这是最重要的参考资料,没有之一。它提倡要在设计的早期阶段就要排除问题,越到后期时序的改善就越困难。其中HLS层次对性能的影响是最大的。

使用 Xilinx 推荐的基线程序逐步满足时序收敛要求。