基于Xilinx的时序分析与约束(5)----衍生时钟约束

judy 在 周三, 01/04/2023 - 10:38 提交

衍生时钟约束必须指定时钟源,在对衍生时钟进行约束时,并不指直接对其周期

衍生时钟约束必须指定时钟源,在对衍生时钟进行约束时,并不指直接对其周期

主时钟约束,就是我们对主时钟(Primary Clock)的时钟周期进行约束

顾名思义,output_delay就是指输出端口的数据相对于参数时钟边沿的延时。

对于7系列FPGA,需要对GT的这两个时钟手工约束:对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

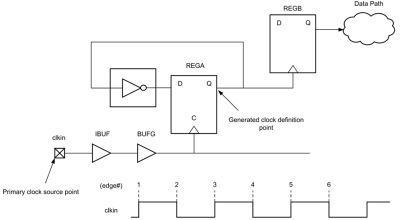

为了获得最佳精度路径覆盖信息,必须正确定义时钟。

时钟要定义在时钟树的根 pin 或 port 上,称为 source point。

时钟的边缘应该由周期和波形进行组合描述。

周期使用纳秒做为单位进行定义。它对应于波形重复的时间。

Vivado会自动设别出两个主时钟,其中clk_pin_p是200MHz,这个是直接输入到了MMCM中,因此会自动约束;另一个输入时钟clk_in2没有约束,需要我们手动进行约束。

XDC 是 Xilinx Design Constraints 的简写,但其基础语法来源于业界统一的约束规范SDC。XDC 在本质上就是 Tcl 语言,但其仅支持基本的 Tcl 语法如变量、列表和运算符等等,对其它复杂的循环以及文件 I/O 等语法可以通过在 Vivado 中 source 一个 Tcl 文件的方式来补充。

时序不满足约束,会导致以下问题:编译时间长的令人绝望;运行结果靠运气——时对时错。

在数字设计中,时钟代表从寄存器(register)到寄存器可靠传输数据的时间基准。Xilinx Vivado集成设计环境(IDE)时序引擎使用ClocK特征计算时序路径要求,并通过松弛计算报告设计时序裕度(Slack)。

上一篇讲述了对时钟的约束方法,时钟不仅对设计很重要,约束情况也很多、很复杂,需要一定的经验。本文将讲述另一种重要的约束:I/O延迟,但与时钟约束相比就简单的多,本文篇幅也相对较少。