基于FPGA的硬件加速之路

judy 在 周三, 08/24/2022 - 09:45 提交

用FPGA来做硬件加速,也有十年的时间了,最近我在回顾这些年的项目经历时,突然有了一个想法

用FPGA来做硬件加速,也有十年的时间了,最近我在回顾这些年的项目经历时,突然有了一个想法

该项目基于AMD Xilinx Varium C1100 FPGA加速卡,为 Filecoin 区块链应用中的Poseidon哈希算法提供了一套完整的硬件加速方案。

使用在 ULTRA96V2 上运行的深度神经网络在 LiDAR 点云中进行 3D 对象检测的端到端演示。

零知识密码学是计算机科学领域在近 50 年间最引人注目的创新之一。零知识证明的一系列先天优势使其成为了各种区块链扩容和隐私解决方案的重要组成部分

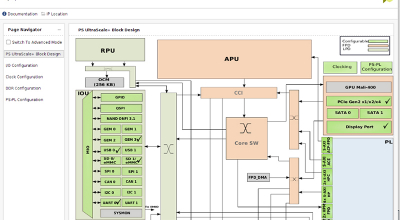

RIFFA 是一种开源通信架构,它允许通过 PCIe 在用户的 FPGA IP 内核和 CPU 的主存储器之间实时交换数据。为了建立其逻辑通道,RIFFA 在 CPU 端拥有一系列软件库,在 FPGA 端拥有 IP 核。本文主要针对其中的DMA性能(Scatter-Gather DMA)进行测试。

基于Vitis硬件加速平台测试用例-vector-add

变革性的高性能应用设计似乎令人望而却步,但凭借自适应计算,您可优化硬件以实现更高的效率,并以超出预期的速度将创新成果推向市场。本视频将为您揭晓...

在开发一个加速程序的之前,有一个很重要的步骤:正确设计程序架构。开发人员需要明确软件应用程序中哪一部分是需要硬件加速的,并且它多少的并行量,以保证硬件加速器件(FPGA)能完美发挥其作用。本文将分为5个步骤来介绍

本文针对上海证券交易所的行情发布系统,采用Verilog硬件描述语言,在FPGA加速卡上开发了对行情信息流的以太网,IP和UDP以及FAST协议的硬件解码,设计了支持指令集编程的微指令加速引擎。与传统的基于软件的方法相比,本文提出的专用硬件处理方案延时可降低10倍以上。

本文针对上海证券交易所的行情发布系统,采用Verilog硬件描述语言,在FPGA加速卡上开发了对行情信息流的以太网,IP和UDP以及FAST协议的硬件解码,设计了支持指令集编程的微指令加速引擎。与传统的基于软件的方法相比,本文提出的专用硬件处理方案延时可降低10倍以上。