利用Vitis开发基于ZCU106的神经网络加速器(二)——DPU编译及Demo

guanxiao_505740 在 周二, 07/27/2021 - 14:35 提交

上一篇文章讲到了如何生成可供Vitis使用的XRT platform。这次我们使用生成的platform来开发一个完整的加速器Demo并在ZCU06上跑通。

上一篇文章讲到了如何生成可供Vitis使用的XRT platform。这次我们使用生成的platform来开发一个完整的加速器Demo并在ZCU06上跑通。

神经网络加速器基本上是一个中介拓扑架构的神经网络加速器,其通过指令解析模块将不同指令分发到不同的数据处理模块。这些数据处理模块共享片上的存储。这种结构的优点有:

神经网络中涉及到大量的张量运算,比如卷积,矩阵乘法,向量点乘,求和等。神经网络加速器就是针对张量运算来设计的。一个神经网络加速器通常都包含一个张量计算阵列,以及数据收发控制,共同来完成诸如矩阵乘法,卷积等计算任务

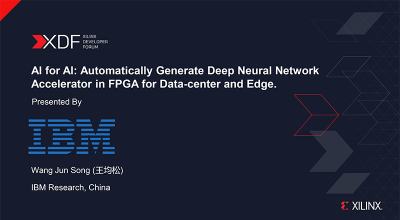

AI 对 AI:在 FPGA 中为数据中心及端点自动生成深度神经网络加速器