异步FIFO设计思路,阅读并理解这篇文章,你可称为异步FIFO大拿

judy 在 周三, 09/13/2023 - 09:24 提交

异步FIFO通常用于跨时钟域处理,是逻辑设计常用基础模块

异步FIFO通常用于跨时钟域处理,是逻辑设计常用基础模块

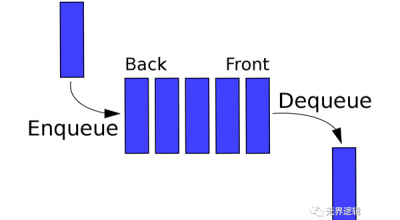

FIFO:First in, first out,先进先出;其主要作用是:数据缓存

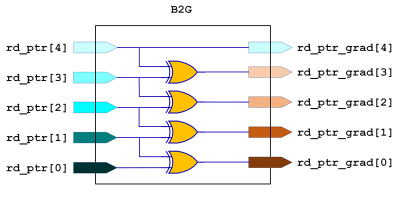

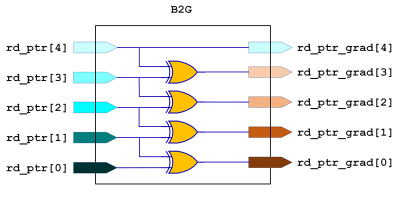

格雷码是一种反射二进制码编码方式

多bit信号跨时钟域的处理方法之一是握手法,也可以称作应答法

多bit信号跨时钟域如何处理呢?为什么不能使用两级打拍的方式呢?

最近看手底下的小伙子们写代码,对于跨时钟域的处理极度的不规范

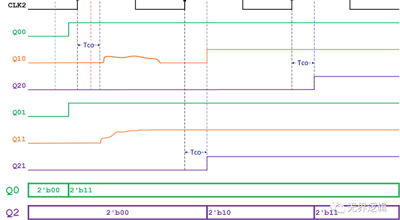

FPGA内容的设计大都是以同步电路为基础,而同步电路的触发则需要统一时钟。时钟信号彷佛是电路的“心跳”,统一给“被管理的”触发器提供血液

FPGA中跨异步时钟处理的方法,是面试中经常碰到的问题,也是我们平时工作中经常会碰到的场景,对于单bit的跨异步时钟处理,我们最常用的方法就是打两拍,但这时这两级寄存器最好是放到同一个Slice中,比如下面的代码