FPGA高速信号处理的片外静态时序分析

francis zhang 在 周五, 12/30/2022 - 09:02 提交

本文作为在高速信号处理时信号输入输出的理论参考

本文作为在高速信号处理时信号输入输出的理论参考

任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本

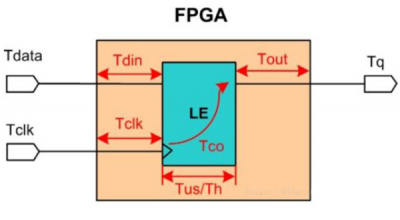

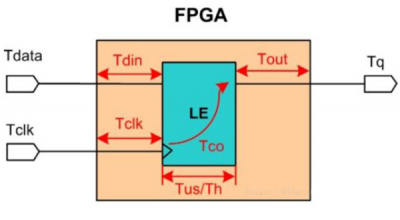

任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本,内容又不那么一致,为了彻底解决这个问题,我研究了一天,终于找到了一种很简单的解读办法,可以看透它的本质,而且不需要再记复杂的公式了。

静态时序分析是检查IC系统时序是否满足要求的主要手段。以往时序的验证依赖于仿真,采用仿真的方法,覆盖率跟所施加的激励有关,有些时序违例会被忽略。此外,仿真方法效率非常的低,会大大延长产品的开发周期。静态时序分析工具很好地解决了这两个问题。

建立时间,保持时间

为了确保寄存器在时钟沿稳定采集数据,那么必须要满足寄存器的建立,保持时间要求。

建立时间要求:在寄存器有效时钟沿之前至少Tsetup时间,数据必须到达且稳定。如下图所示。