支持AI视频处理的高容量流媒体加速卡方案

judy 在 周一, 08/28/2023 - 16:42 提交

本文分享MA35D的基本架构和功能,以及该卡在各个领域视频解决方案中的应用

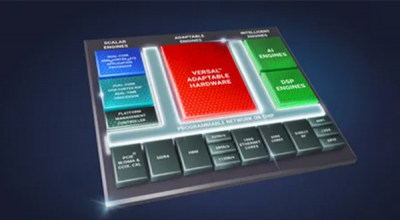

ACAP(Adaptive Compute Acceleration Platform)是赛灵思(Xilinx)公司提出的概念,表示一种自适应计算加速平台。ACAP 是在 FPGA(可编程门阵列)的基础上演进而来的,结合了 FPGA 的灵活性和可编程性以及 ASIC(专用集成电路)的性能和效率。

ACAP 旨在应对多样化、动态性和高度定制化的计算需求。与传统的 FPGA 不同,ACAP 具有更高级别的自适应性,能够在运行时重新配置其硬件架构,以适应不同的工作负载。这种动态适应性使得 ACAP 在处理各种任务时能够更加高效地利用硬件资源。

本文分享MA35D的基本架构和功能,以及该卡在各个领域视频解决方案中的应用

本文探讨了身处更大规模的沉浸式媒体技术的前沿,8K 分辨率在当下的应用原因和用处

为了获取和传输 8K 视频,接口必须提供 4 倍于其 4K 前代产品的带宽

音频/视频(A/V)接口是任何显示系统不可或缺的一部分

本文将探讨为何采用 8K 视频、其优势和潜在缺点

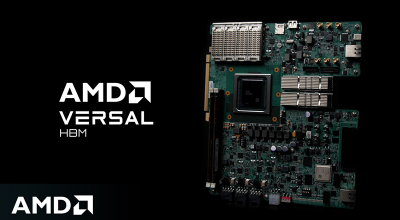

本视频重点介绍了 VHK158 评估套件提供的关键板载接口和组件以及配件

关于PRBS13、QPRBS13、PRBS13Q和QPRBS13-CEI的定义

本文着重讲解某些包中的 112G 长距 (LR) GTM 操作的通道选择要求