数据中心加速芯片需求大爆发,FPGA正领跑市场

judy 在 周三, 12/14/2022 - 17:37 提交

本文我们就来具体看一下,为什么FPGA能够在数据中心加速领域领跑?具体的优势有哪些?

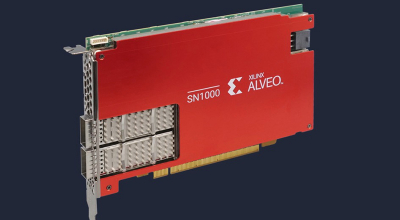

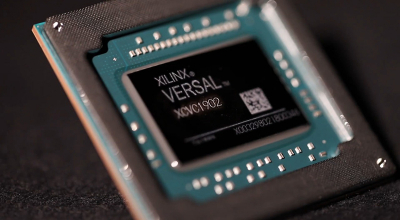

ACAP(Adaptive Compute Acceleration Platform)是赛灵思(Xilinx)公司提出的概念,表示一种自适应计算加速平台。ACAP 是在 FPGA(可编程门阵列)的基础上演进而来的,结合了 FPGA 的灵活性和可编程性以及 ASIC(专用集成电路)的性能和效率。

ACAP 旨在应对多样化、动态性和高度定制化的计算需求。与传统的 FPGA 不同,ACAP 具有更高级别的自适应性,能够在运行时重新配置其硬件架构,以适应不同的工作负载。这种动态适应性使得 ACAP 在处理各种任务时能够更加高效地利用硬件资源。

本文我们就来具体看一下,为什么FPGA能够在数据中心加速领域领跑?具体的优势有哪些?

新的8 GB版本在同样小巧和管脚兼容的外形尺寸之下将存储密度提高了一倍

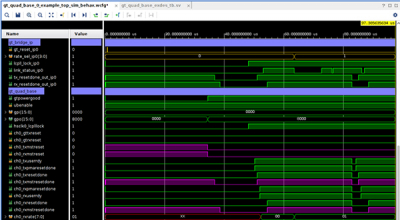

本篇博文侧重于提供 Versal™ GTY 仿真示例、演示 GTY 如何解复位以及如何执行速率变更。

了解 Versal 器件功耗估计从 XPE 迁移到 PDM 的简易迁移路径,并展示了其易用性和增强型向导。

本研讨会将演示如何使用可编程逻辑和 AI 引擎阵列功能对设计开展早期功能验证。

本文档聚焦 AI 引擎内核编程,除单内核编程外,还涵盖了多方面的内容

Vitis 视觉 AIE 设计方法有助于设计人员利用 Vitis 视觉 AIE 库的功能,该功能主要针对 Versal 自适应计算加速平台 (ACAP)

AMD 近期已开始出货 Versal® AI Edge VE1752 ACAP 预生产器件。

下一代 7nm 工艺 Versal 实现 4 路 2MP,2 路 8MP 30FPS 相机,1 路激光雷达,1 路毫米波雷达的数据通道处理

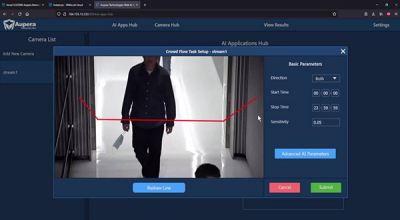

本视频演示如何开始使用在 VMAccel FPGA 云上的 VCK5000 Aupera 视频机器学习流媒体服务器解决方案 2.0。