上海磐矽采用国微思尔芯最新双核S7-VU19P逻辑系统,加速芯片验证

judy 在 周五, 09/03/2021 - 09:46 提交

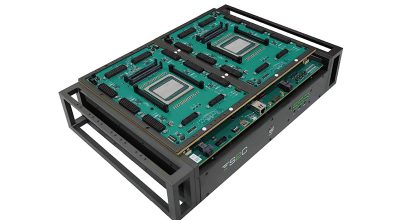

双核S7-VU19P逻辑系统配置了双颗赛灵思 UltraScale+ VU19P FPGA,多套逻辑系统可堆叠或机架部署,以支持更大逻辑规模的设计。搭配芯神瞳协同仿真套件轻松实现将设计链接到原型验证环境,允许大量的事务级数据在 FPGA 与 PC 主机之间进行交互;同时可选配内置的深度调试套件 MDM Pro,用于多颗FPGA的深度调试

双核S7-VU19P逻辑系统配置了双颗赛灵思 UltraScale+ VU19P FPGA,多套逻辑系统可堆叠或机架部署,以支持更大逻辑规模的设计。搭配芯神瞳协同仿真套件轻松实现将设计链接到原型验证环境,允许大量的事务级数据在 FPGA 与 PC 主机之间进行交互;同时可选配内置的深度调试套件 MDM Pro,用于多颗FPGA的深度调试

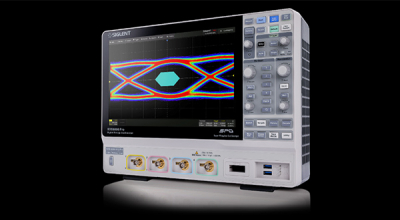

Kintex UltraScale+ 拥有的高速 SerDes,大大简化了 PCB 设计、节约了 PCB 面积;其片内集成大量 Block RAM、UltraRAM,替代了传统方案中的多片外挂 QDR SRAM,从而大幅节省 IO 资源和 PCB 面积。Kintex 器件所拥有的高速处理时钟和丰富的 DSP 资源,满足了数字示波器宽带实时数字信号处理,复杂滤波,高速 FFT 需求。

本文描述了在为UltraScale+™设备使用动态功能交换时,如何改善编译时间并提高设计安全性。

作为全球唯一基于16纳米技术的成本优化型产品组合,UltraScale+ 器件采用台积电最先进的InFO(Integrated Fan Out,集成扇出)封装技术。借助InFO技术,UltraScale+ 器件能以紧凑的封装提供高计算密度、出色的性能功耗比以及可扩展性,从而应对智能边缘应用的需求。

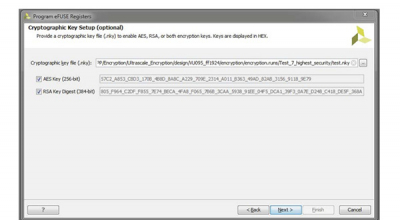

本文描述了使用 Vivado® 设计套件生成加密位流和加密密钥的分步过程。

Xilinx公司采用InFO封装的新型Zynq UltraScale+ MPSoC实现了全方位的工业性能--所有这些器件都采用了具有高计算密度的紧凑外形。

了解全新的 16nm Artix® UltraScale+™ FPGA 系列和 Zynq® UltraScale+ MPSoC ZU1 器件,以超紧凑的封装提供,可为成本敏感型的边缘和网络应用提供无与伦比的计算密度。

一图读懂赛灵思全新UltraScale+成本优化型产品组合

赛灵思今日宣布面向市场扩展其 UltraScale+ 产品组合,以支持需要超紧凑及智能边缘解决方案的新型应用。新款 Artix® 和 Zynq® UltraScale+ 器件的外形尺寸较传统芯片封装缩小了70%,能够满足工业、视觉、医疗、广播、消费、汽车和互联市场等更广泛的应用领域。

P4改变了网络格局,因为它允许表达自定义数据包处理。近年来,有几篇著作将P4程序映射到FPGA。但是,这些工作大部分都集中在实现数据包解析器或match action阶段。迄今为止,尚未有报道提出关于FPGA的通用数据包逆解析的原理。推荐一篇2021年FPGA顶会会议论文,介绍基于FPGA开源200Gbps数据包逆解析器的设计与实现。