【干货分享】优化rootfs的大小

judy 在 周日, 09/27/2020 - 14:41 提交

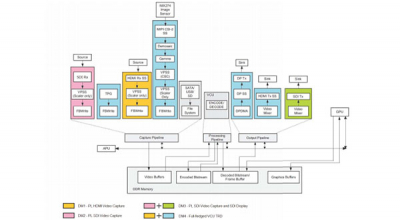

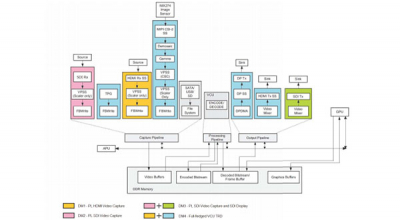

Xilinx VCU TRD 集成了图像和视频编解码功能,生成的根文件系统比较大,2020.1的rootfs.cpio.gz大约有114MB。工程师可以根据自己需要裁剪,减少根文件系统大小。

在Ubuntu下,解压rootfs.cpio.gz,得到rootfs.cpio,再解压,得到就是文件了。

Zynq® UltraScale+™ MPSoC(多处理器系统芯片)是赛灵思(Xilinx)推出的一款集成了处理器系统和可编程逻辑的器件。这一系列芯片采用 UltraScale+ 架构,结合 ARM 处理器和可编程逻辑,为嵌入式系统提供了灵活性和高性能。

Zynq UltraScale+ MPSoC 适用于嵌入式系统设计,特别是对于需要高度定制和硬件加速的应用。它为设计人员提供了处理器和 FPGA 的集成解决方案,以满足各种复杂系统的需求。

Xilinx VCU TRD 集成了图像和视频编解码功能,生成的根文件系统比较大,2020.1的rootfs.cpio.gz大约有114MB。工程师可以根据自己需要裁剪,减少根文件系统大小。

在Ubuntu下,解压rootfs.cpio.gz,得到rootfs.cpio,再解压,得到就是文件了。

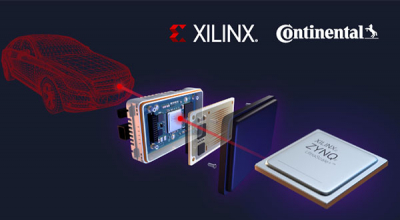

赛灵思和大陆集团今日宣布将通过 Zynq® UltraScale+™ MPSoC 平台支持大陆集团开发新款高级雷达传感器 (ARS) 540,联手打造汽车行业首款量产版 4D 成像传感器

赛灵思将通过 Zynq® UltraScale+™ MPSoC 平台支持大陆集团开发新款高级雷达传感器( ARS ) 540,联手打造汽车行业首款量产版 4D 成像传感器。双方的合作将助力配备 ARS540 的新车型实现 SAE J3016™ L2 功能,为迈向 L5 自动驾驶系统铺平道路。

赛灵思为 FPGA 和 MPSoC 器件中所有受支持的 I/O 标准提供了 I/O 缓存信息规范 (I/O Buffer Information Specification, IBIS) 模型。本篇博文旨在提供有关如何为可编程逻辑 (PL) 和处理器系统 (PS) 多用途 I/O (MIO) 进行 IBIS 模型名称解码的指导信息。

有工程师反映,根据MPSoC SWDT在Standalone下的例子xwdtps_polled_example.c,不能实现MPSoC的PS复位。

MPSoC是Xilinx基于16nm工艺推出的异构计算平台,由于灵活、稳定,在业界得到了广泛的使用。异构计算是一个比较新的领域,需要协调硬件设计、逻辑设计、软件设计,对工程师的要求很高。实际设计过程中,很多工程师对实现PS/PL之间的数据交互感到头疼。本文将介绍主要的PS/PL之间的数据交互办法。

Xilinx Zynq® UltraScale+™ MPSoC 技术助力斯巴鲁基于视觉的高级驾驶辅助系统(ADAS)新一代 EyeSight。集成在全新斯巴鲁 Levorg 车型的新版 EyeSight 系统,将为其提供包括自适应巡航控制、行车道保持辅助和预碰撞制动等先进特性,将一流的安全技术交付至消费者手中。

本文提供了在Zynq® UltraScale+™器件中对BBRAM和eFUSEs进行自我编程的方法。

在《Zynq UltraScale+ MPSoC 数据手册》(DS925) 中,XAZU7EV-1Q 器件与 XAZU11EG-1Q 器件的最低量产软件和速度规格已从 Vivado 工具 2019.1.1 v1.26 更新至 Vivado 工具 2020.1.1 v1.30。

一站式赛灵思工业、视觉与医疗资源库建设完成,我们将涉及工业、视觉与医疗应用领域的相关技术文档、视频资源汇集整理奉献给广大同行业者