Vitis 库流程 - 在 Zynq 裸机设计中使用视觉库 L1 remap 函数的示例

judy 在 周一, 07/31/2023 - 11:31 提交

本文演示如何在 Zynq 设计中使用 Vitis 视觉库函数 (remap) 作为 HLS IP

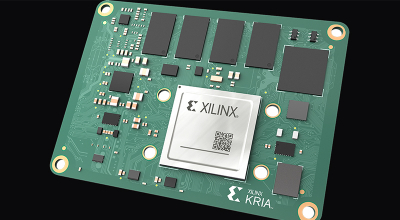

Zynq® UltraScale+™ MPSoC(多处理器系统芯片)是赛灵思(Xilinx)推出的一款集成了处理器系统和可编程逻辑的器件。这一系列芯片采用 UltraScale+ 架构,结合 ARM 处理器和可编程逻辑,为嵌入式系统提供了灵活性和高性能。

Zynq UltraScale+ MPSoC 适用于嵌入式系统设计,特别是对于需要高度定制和硬件加速的应用。它为设计人员提供了处理器和 FPGA 的集成解决方案,以满足各种复杂系统的需求。

本文演示如何在 Zynq 设计中使用 Vitis 视觉库函数 (remap) 作为 HLS IP

AMD ZCU106 U-Boot 2023.1 Open Source Flow 编译的缺少“gnutls/gnutls.h”错误

FPGA技术被广泛的应用在VR应用中或是其相关的研发项目中

本文介绍了医疗设备设计中的功能安全和网络安全方法

AUMO 提供基于AMD Xilinx FPGA Zynq UltraScale+MPSoC 的自动驾驶车辆采集计算

在云计算之后,边缘计算将成为未来十年物联网市场新的增长点

每个模块的 GTH 规格略有不同。相比于商用级 K26C,工业级 K26I 存在一些限制

客户为AMD Xilinx SoC创建了PetaLinux工程。需要定制PetaLinux中的FSBL

Multi-Scaler是一个用于图像缩放的视频处理IP核,支持最多8路输出