Vivado Hardware Debug技巧 如何在IBERT眼图上添加模板

judy 在 周四, 06/01/2023 - 15:55 提交

在Vivado的IP Catelog中找到IBERT,此处以UltraScale Plus系列的GTY为例

Vivado是赛灵思(Xilinx)公司推出的一款集成开发环境(IDE),用于设计和开发基于FPGA(可编程逻辑器件)的数字电路。Vivado提供了一个全面的工具套件,支持从设计到验证、实现和编程的全过程。

Vivado是一种全面的FPGA设计工具,适用于各种应用,包括通信、图像处理、数字信号处理、网络加速和嵌入式系统设计。

在Vivado的IP Catelog中找到IBERT,此处以UltraScale Plus系列的GTY为例

对 Versal 设计使用 Vivado DFX 时出现硬件故障,我怎样才能避免这种情况?

使用Intelligent Design Runs,Versal™ 自适应 SoC 的平均 QoR 提升 8%

当我尝试在机器上安装 Vivado 时,无法通过帐户身份验证检查。为什么会出现此问题?

在 Vivado 2022.2 中使用 Advanced I/O Wizard 并配置源同步 TX+RX 接口时

如果需要,我是否需要购买完整的 Vivado 许可证,才能使用 SDK,目前是否还有其它类型的许可证可用?

当使用第三方综合器比如 Synopsys® Synplify Pro或Mentor® Graphics Precision 来综合

使用“时钟校准去歪斜”时,在 Vivado 中会显示下列消息以指明是否启用该功能特性

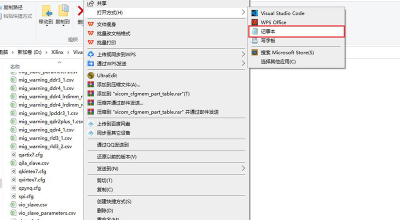

找到[安装目录]\2021.1\data\xicom下的xicom_cfgmem_part_table.csv文件

本文提供了仿真进程以及 Vivado® Design Suite 中的仿真选项的概述