使用加密和身份验证来保护 UltraScale/UltraScale+ FPGA 比特流的应用说明

judy 在 周二, 07/13/2021 - 09:38 提交

描述使用 Vivado® Design Suite 生成加密比特流和加密密钥的分步过程。

Vivado是赛灵思(Xilinx)公司推出的一款集成开发环境(IDE),用于设计和开发基于FPGA(可编程逻辑器件)的数字电路。Vivado提供了一个全面的工具套件,支持从设计到验证、实现和编程的全过程。

Vivado是一种全面的FPGA设计工具,适用于各种应用,包括通信、图像处理、数字信号处理、网络加速和嵌入式系统设计。

描述使用 Vivado® Design Suite 生成加密比特流和加密密钥的分步过程。

了解块设计容器及其兼容性。

当今的设计突破了器件容量和性能的极限,常常为及时满足设计目标带来艰巨的挑战。了解 UFDM(超快设计方法)的最新发展,这是一系列基于工厂专家经验的最佳实践,在过去几年里他们帮助客户解决了最棘手的设计收敛问题,并获得了最佳结果质量。同时,还可了解非常实用的 Vivado 综合与实现技巧,以提升生产力。

赛灵思近日宣布推出 Vivado® ML 版,这是业内首个基于机器学习(ML )优化算法以及先进的面向团队协作的设计流程打造的 FPGA EDA 工具套件,可以显著节省设计时间与成本,与目前的 Vivado HLx 版本相比,Vivado ML 版将复杂设计的编译时间缩短了 5 倍,同时还提供了突破性的平均达 10% 的结果质量( QoR )提升。

了解如何在 2021.1 中大幅简化 IP 版本控制

Xilinx推出具有突破性技术的 Vivado ML 以加速设计收敛并提升 QoR,以及先进的 DFX 功能,可实现时间计算的创新形式。

赛灵思公司今日宣布推出 Vivado® ML 版,这是业内首个基于机器学习( ML )优化算法以及先进的面向团队协作的设计流程打造的 FPGA EDA 工具套件,可以显著节省设计时间与成本。与目前的 Vivado HLx 版本相比,Vivado ML 版将复杂设计的编译时间缩短了 5 倍,同时还提供了突破性的平均达 10% 的结果质量( QoR )提升。

本视频着重介绍了 Vivado Design Suite 2020.2 版中的新增功能,包括操作系统和器件支持、高级别增强功能以及加速设计集成、实现与验证相关的各项改进措施。

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado 2020.2为例,讨论如何升级Vivado工程脚本。

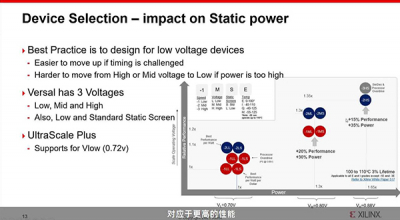

本视频讨论功耗约束以及报告功耗估算的最佳实践。