Versal- 在一个triplet中实现DDRMC和soft DDR4 controller

judy 在 周五, 03/29/2024 - 15:17 提交

在非常多的客户应用工程中,都会用到DDR4/LPDDR4来存取大容量数据

在非常多的客户应用工程中,都会用到DDR4/LPDDR4来存取大容量数据

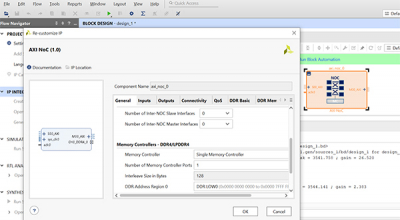

本实验通过PL端Verilog代码直接读写ddr4,主要了解NoC的配置方法

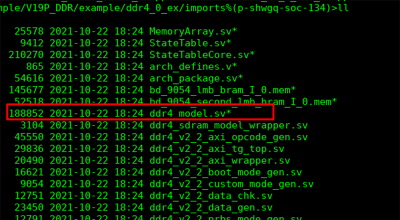

首先新建ddr的IP,具体每个参数的含义,可以参考之前写的《Virtex7 Microblaze下DDR3测试再右键》,打开IP的Example Design

今天我们来介绍一下I/O planning方面的设计考虑和实现流程。

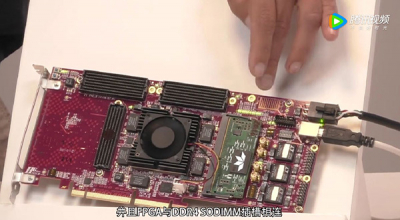

观看这个短视频,了解如何连接Teledyne e2v耐辐射DDR4存储器与AMD XILINX Kintex Ultrascale FPGA KU115。

在这个短视频中,您将学习如何设置DDR4 控制器IP,以连接Teledyne e2v DDR4产品和Xilinx的可编程逻辑器件。

本篇博客将为您演示如何使用此报告来帮助加速调试,甚至完全避免硬件故障,最后确定此问题根本原因是校准完成时出现争用状况。出现争用状况的原因是由于某个多周期约束所覆盖的时序例外,由此导致在时序分析报告中并未标记此问题。

本篇博文中的分析是根据真实客户问题撰写的,该客户发现硬件中存在 DDR4 校准错误,不同板以及不同构建 (build) 之间出现的故障并不一致。本篇博文旨在演示用于缩小根本原因范围以及修复此问题的部分调试技巧。

本文将重点介绍 PolarFire FPGA 和 Teledyne e2v DDR4T04G72 之间点对点的连接的例子,以及多个 DDR4器件如何与一片 Xilinx KU060 FPGA 连接。

在基于供电网络 (PDN) 的共振峰创建的布局前、布局后和系统验证数据模式中分析电源完整性对 FPGA DDR4存储器接口中的信号完整性的影响。使用 FPGA 配置的矢量网络分析仪 (VNA) 测量 PDN 阻抗曲线。创建多个测试数据模式,以便将电源的电流频谱分量与 PDN 共振峰叠加在一起,并演练传输线多次反射累积效应