Teledyne e2v:通过杂散抑制IP,立即将宽带ADC的动态性能提高约10 dBFS

judy 在 周一, 06/20/2022 - 09:47 提交

DX4 - 与Xilinx Kintex® Ultrascale FPGA兼容的后处理算法可在宽带应用中提供高达10 dBFS的SFDR动态杂散抑制和接近1个有效位的额外分辨率。

DX4 - 与Xilinx Kintex® Ultrascale FPGA兼容的后处理算法可在宽带应用中提供高达10 dBFS的SFDR动态杂散抑制和接近1个有效位的额外分辨率。

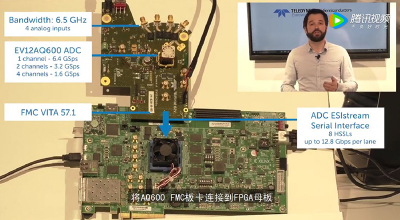

您将学习如何简单地下载并创建Vivado工程,实现ADC EV12AQ600/605的串行接口,并缩短您的开发时间。

本视频带您学习如何简单地下载并创建Vivado工程,实现ADC EV12AQ600/605的串行接口,并缩短您的开发时间。

实现确定性延迟是当今许多系统设计中讨论的主题。过去,人们一直在努力提高数据传输速度和带宽。如今的应用则越来越重视确定性——即要求数据包在精确的、可重复的时间点传送。本文将在设备的层面讨论确定性这一主题,以及如何设计超高速数据转换和信号处理系统以保证确定性延迟。