Matlab生成fir滤波器抽头系数

judy 在 周三, 03/27/2024 - 10:25 提交

在Vivado调用fir滤波器时,我们会遇到需要填充滤波器抽头系数的问题

在Vivado调用fir滤波器时,我们会遇到需要填充滤波器抽头系数的问题

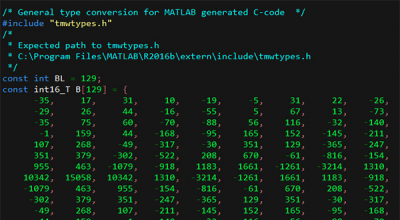

该项目介绍了如何使用 Verilog 实现具有预生成系数的简单 FIR 滤波器。

本讲使用两个 DDS 产生待滤波的信号和matlab产生带滤波信号,结合 FIR 滤波器搭建一个信号产生及滤波的系统,并编写 testbench 进行仿真分析,第五讲、第六讲开始编写 verilog 代码设计FIR滤波器,不再调用IP核。

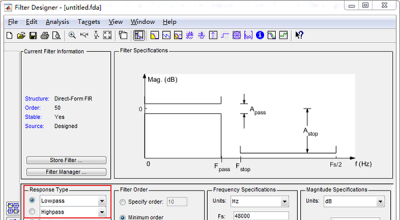

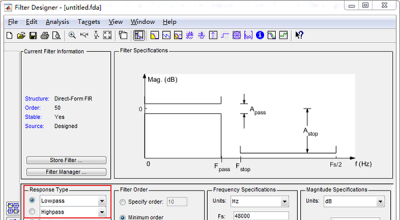

本文以99阶FIR低通滤波器为例,学习使用matlab的fdatool工具箱设计滤波器,并将滤波器系数导出到.coe文件,联合Vivado进行FPGA的FIR滤波器设计

我们上一篇文章的混频是8MHz与5MHz的相乘,所以我们这篇文章的目的是设计一个低通滤波器滤除13MHz的成分。FIR的设计方法在数字信号处理中有两种方法,最常用的就是窗函数法。这里我们将使用汉明窗进行进一步的设计。

滤波器是一种用来减少,消除干扰的电器部件,有对特定频率的频点或该频点以外的频率信号进行有效滤除,从而实现消除干扰、获取特定频率信号的功能。数字滤波器相比模拟滤波器,有着更高的精度、信噪比、无可比拟的可靠性。

在Vivado FIR滤波器设计与仿真(一)中产生了两路正弦信号,频率分别为4MHz和5MHz,今天要进行FIR滤波器设计,在进行滤波器设计之前,需要对滤波器的参数进行设置,需要借助MATLAB软件或者Filter Solutions软件,这次使用Filter Solutions来进行参数设定。

本文是该系列的第17篇。上一篇介绍了使用低层次封装的block搭建直接型FIR滤波器结构的方法,对设计进行时序分析,并将设计流水线化来提高系统的工作频率。转置型FIR滤波器是一种由直接型FIR滤波器变换而来的结构,在几乎相同的结构下有着更好的性能,本文将对此做介绍。

转置型FIR滤波器

滤波器结构框图如下: