Vivado布线和生成bit参数设置

judy 在 周四, 09/14/2023 - 09:29 提交

本文主要介绍Vivado布线参数设置

本文主要介绍Vivado布线参数设置

本文将介绍Vivado增量编译的基本概念、优点、使用方法以及注意事项

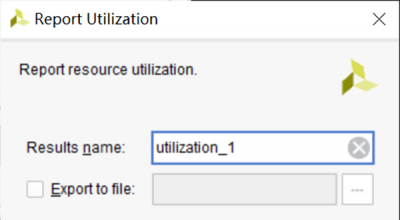

本文介绍Vivado中如何进行FPGA设计资源优化以及查看各子模块资源占用的方法

本文介绍了在AMD Xilinx Zynq平台上实现嵌入式软件和FPGA设计的集成工作流程

面试必问题目,先记几个结论

本文介绍几种常见的反压方式,并给出他们的一些优缺点

Vitis高层次综合可通过在选定的 AMD 器件上将 C/C++ 代码综合为可编程逻辑的 RTL 代码

本文深入探讨在FPGA 设计中要避免的 10 大错误

这里介绍一种新的公平调度方案,和前面的方案相比,最大的特点是不缓存数据

在FPGA设计中,我们通常采用的都是“自顶向下”的设计方法,即现有顶层设计,再有细节设计。