高级FPGA设计之高速率结构设计

judy 在 周一, 03/13/2023 - 15:21 提交

在进行 Verilog 设计中,一般会考虑三个基本参数:速度、面积、功耗

在进行 Verilog 设计中,一般会考虑三个基本参数:速度、面积、功耗

科技即生产力,最近,OpenAI 发布了 ChatGPT,在各大论坛和许多网站上受到了广泛关注

这篇文章主要介绍了 Verilog 在 FPGA 设计中的概念和使用方法

在FPGA开发调试阶段,经常遇到这样的情况,需要临时添加信号,观察信号变化

本文介绍一些计数器的常用方法和注意点

串并、并串转化也是FPGA设计中常见的基本问题,相对来说比较简单

在本文中,您将了解最常见问题的来源及其解决方案,以及如何将这些思想应用到您的设计中

对于FPGA设计,传统设计都是一个FPGA一个设计,产生一个Bit文件。这就是完整bit文件(full bit)

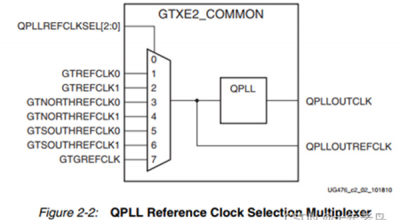

从IP核的时钟配置来学习transceiver的参考时钟架构细节

在FPGA的设计中,不可避免的会用到FIFO和RAM这2个基本单元