Xilinx FPGA资源解析与使用系列——Transceiver(十一)transceiver与用户数据的接口

judy 在 周二, 11/29/2022 - 09:02 提交

本文主要讲transceiver与用户逻辑数据的接口

本文主要讲transceiver与用户逻辑数据的接口

我们主要关注的是TXDIFFCTRL 摆幅、Pre-Emphasis 预加重、Post-Emphasis 去加重

在GTX/GTH收发器 TX链路中有两个内部并行时钟作用于PCS:PMA并行时钟(XCLK)和TXUSRCLK时钟域

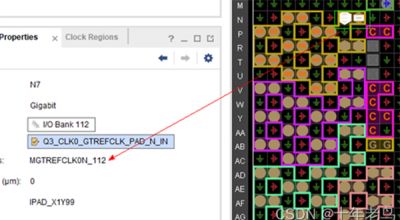

在看手册时,看到最后写到了transceiver的资源信息和位置信息

前面我们理解了TXOUTCLK和RXOUTCLK的源头

本文缕缕时钟到底是哪来的,以及要起什么作用

本文将结合ip example工程来理解transceiver的复位,通过学习记录,力求将其复位过程理解通透

在数字系统设计中,我们传统上都认为,应该对所有的触发器设置一个主复位,这样将大大方便后续的测试工作

Transceiver的环回功能对于调试和定位问题非常重要。环回有四种模式

Xilinx FPGA的资源一般指IOB,CLB,BRAM,DCM,DSP五种资源。其中IOB就是input/output block,完成不同电气特性下对输入输出信号的的驱动和匹配要求。