FPGA时序约束之Vivado辅助工具

judy 在 周三, 07/08/2020 - 10:13 提交

上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合或实现后的Design中打开。

AI初创公司Mipsology正在与Xilinx合作,据说打算让FPGA依靠一个附加命令取代AI加速器中的GPU。Mipsology的“zero effort”软件Zebra可以转换GPU代码,使其能在FPGA上的Mipsology AI计算引擎中运行,同时无需改写任何代码或进行重新训练

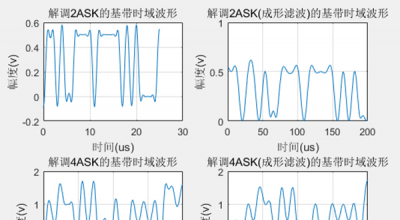

FSK信号的解调也有非相干和相干两种,FSK信号可以看作是用两个频率源交替传输得到的,所以FSK的接收机由两个并联的ASK接收机组成。

如果您正在使用 MATLAB 建模数字信号处理(DSP)或者视频和图像处理算法,并且最终将其用于 FPGA 或 ASIC,本文可能将为你带来帮助。

LFSR:线性反馈移位寄存器(linear feedback shift register, LFSR)是指给定前一状态的输出,将该输出的线性函数再用作输入的移位寄存器。异或运算是最常见的单比特线性函数:对寄存器的某些位进行异或操作后作为输入,再对寄存器中的各比特进行整体移位。

振幅键控信号的解调主要有包络检波和同步检测两种方法,后者又被称为相干解调。相干解调需要提供与输入同频同相的载波信号,通常需要采用锁相环技术实现载波信号的提取,较为复杂,这里采用非相干解调的方法实现ASK解调,只需要将输入信号经过整流滤波即可得到基带信号。

通过上面其他章节的介绍,网口千兆通信,可以使用TCP或者UDP协议,可以外挂PHY片或者不挂PHY片,总结下来就有下面几种方式完成通信

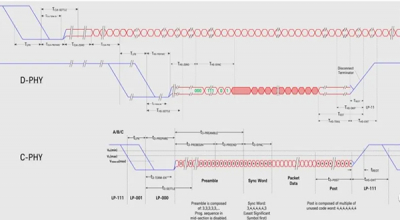

MIPI是移动领域最主流的视频传输接口规范,没有之一,目前应用最广泛的是MIPIDPHY和MIPI CPHY两组协议簇,其中CSI-2主要用于图像接入,DSI-2主要用于图像输出。本文主要以CSI-2为例进行仔细说明,DSI-2雷同,举一反三即可。

如今,在以数据为中心的世界里,网络在数据传输方面的性能正在一步步逼近极限。网络应用需要支持数量不断增多的用户连接、扩大支持的带宽范围、降低它们的时延....

Enyx提供基于FPGA的解决方案,为网络应用的开发提供便利。

现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产;但是许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设计中。解决办法之一是深入研究主要供应商提供的 FPGA 架构及相关工具;本文则从 Xilinx 产品系列开始着手