FPGA的虚拟时钟如何使用?

judy 在 周二, 12/07/2021 - 10:06 提交

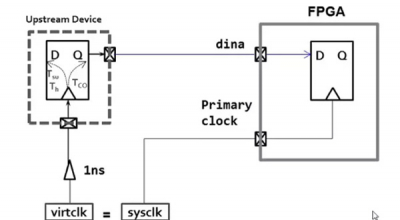

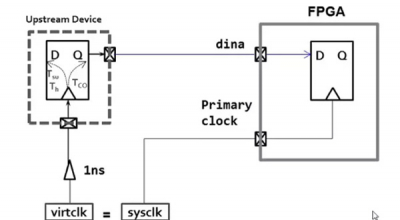

在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟,但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟,但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

对于7系列FPGA,需要对GT的这两个时钟手工约束:对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读写测试

本文以浮点数Floating-point IP核将定点数转换为浮点数为例,详细讲解AXI DMA IP核的使用方法。

FPGA芯片的三个主要资源主要包括可配置逻辑单元(CLB)、存储单元、运算单元、一流的I / O资源和布线资源等。其中,CLB在FPGA中最丰富,在7系列的FPGA中,一个CLB中有两个Slice,Slice中包含4个LUT6、3个数据选择器MUX,两个独立进位链(Carry4,Ultrascale是CARRY8)和8个主轴。这里我们主要介绍Carry4。

在FPGA的开发中,对于两个异步时钟,如果我们可以在RTL的设计中保证这两个时钟域之间的处理都是正确的,那就可以让工具不分析这两个时钟域之间的交互。

对于Xilinx的FPGA,每一片都有一个专门的ID,就像我们的身份证号一样,每个都不一样,Xilinx也形象的把这个ID叫做DNA。7系列以及之前FPGA的DNA有57bit,Ultrascale FPGA的DNA有96bit,Zynq Ultrascale+的FPGA有两个DNA,PL端一个,PS端也有一个。

分享面试中经常遇到的5个FPGA基本概念

FPGA中跨异步时钟处理的方法,是面试中经常碰到的问题,也是我们平时工作中经常会碰到的场景,对于单bit的跨异步时钟处理,我们最常用的方法就是打两拍,但这时这两级寄存器最好是放到同一个Slice中,比如下面的代码

单片机的硬件串口,发送和接收完毕都有相应的标志位,例如TC(发送完成)和RXNE(接收完成)位。FPGA则不同,FPGA采用的是AXI4-Stream协议,数据送入IP核后,经过固定数量的时钟周期后,就得到运算结果,没有任何标志位表明运算完成。