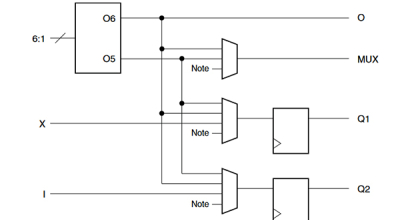

UltraScale FPGA 可编程逻辑块(CLB)

guanxiao_505740 在 周二, 01/30/2024 - 09:32 提交

本文为作者对AMD UltraScale FPGA可编程逻辑块的资源和设计方法的学习笔记

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

本文为作者对AMD UltraScale FPGA可编程逻辑块的资源和设计方法的学习笔记

本文将介绍一下RGB与HSV互转

对FPGA的管脚进行约束的时候,常常看到这样的电平标准

在 FPGA 上实现了 JPEG 压缩和 UDP 以太网传输

本文将详细介绍图像灰度反转与彩色反转的基本概念以及FPGA实现

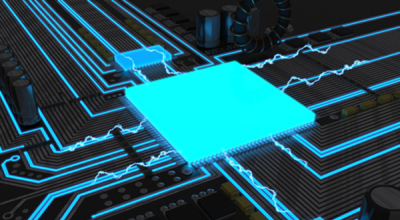

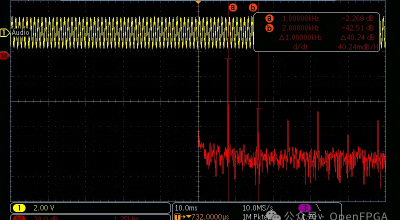

本文介绍了如何从 SD 卡读取音频文件并将其输出到扬声器上

本文将详细介绍图像平移算法

本文介绍了时钟设计方案中的每个部分,并推荐了一些设计方法。

FPGA的IO电平标准涉及到其输入和输出引脚的电压电平范围,以确保与其他器件和系统的互操作性

本文将介绍适用于基于FPGA的网络设备的IEEE 1588透明时钟架构,帮助您实现精确时间同步和高效通信。