如果FPGA/微处理器上只剩下一个GPIO,该如何进行模拟测量?

judy 在 周四, 10/26/2023 - 17:56 提交

本文将探讨一种温度-频率转换器

本文将探讨一种温度-频率转换器

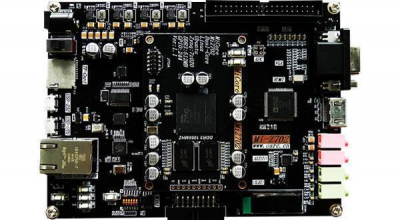

在使用ZYNQ进行开发设计时,往往需要对一些GPIO引脚进行配置,传统的配置方法通常在PL端进行管脚约束之后在Verilog代码中对相应引脚进行配置。这样如果开发过程中一旦有需要对管脚配置进行修改的话,那么就必须重新进行综合、布局布线、生成比特流文件,如果设计工程相对复杂的话,完成整个过程通常需要相当长一段时间。影响开发效率。

本文提供Ultra96 board相关文档下载(开发板介绍/原理图/硬件使用手册/参考设计等有用资源)

Zynq-7000和MPSoC有很多MIO管脚。如果外设有中断,也可以通过MIO驱动。

Xlinx的ZYNQ系列SOC集成了APU、各种专用外设资源和传统的FPGA逻辑,为ARM+FPGA的应用提供助力,降低功耗和硬件设计难度的同时极大提高两者间传输的带宽。之前在研究生课题中使用过ZYNQ搭建环路系统对算法进行板级验证

首先来理清楚MIO与EMIO的关系。MIO是PS的I/O引脚,一共有54个,分为Bank0与Bank1,可以接许多外设比如UART、SPI或GPIO等,另外可以引脚复用。

EMIO就是PS控制PL资源的简单例子。EMIO就是可扩展的MIO,当与PS直接相连的MIO不够用时,可以使用EMIO做“扩展”。使用体会上,感觉就是ARM直接控制了PL部分的管脚。GPIO的bank2和bank3就是通过EMIO接口与PL相连的,本文将先通过PS控制PL部分流水灯的实例感受下EMIO的使用,然后再介绍EMIO相关的基本概念

ZYNQ的GPIO由4个BANK组成,其体系结构如图1所示。其中Bank0有32个GPIO引脚,Bank1有22个引脚,共54个GPIO引脚直接通过MIO连接到PS上,每个引脚可以通过寄存器的设置来确定该引脚为输入、输出或者中断,因为54个MIO引脚直接连接在PS上,像其他普通ARM一样,不需要通过XPS进行硬件配置,直接通过SDK编程即可

本文将介绍PS部分GPIO中MIO的使用。本文先通过一个控制LED闪烁的实例体会MIO的用法,学习GPIO相关结构体与API函数的使用;然后再系统讲解GPIO的相关概念。

ZYNQ7000 系列芯片有54个MIO(multiuse I/O),它们分配在GPIO的Bank0和NBank1 隶属于PS的部分,这些IO与PS直接相连。不需要添加引脚约束,MIO信号对PL部分是透明的,不可见。所以对MIO的操作可以看是对纯PS的操作