UltraScale+ 器件 Integrated Block for PCI Express 产品指南(v1.3)

judy 在 周四, 03/23/2023 - 09:24 提交

该核属于高带宽、高可缩放性且高可靠性的串行互连构建块解决方案,适用于基于UltraScale+™架构的器件。

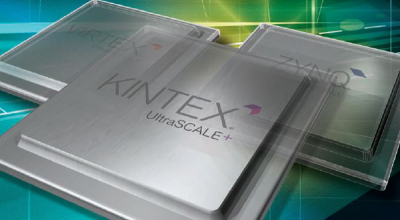

随着现在FPGA工作的时钟频率越来越高,高速接口越来越多,即便容量达到十几Mb的数量级

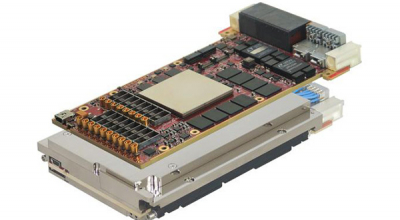

Abaco Systems 基于AMD-赛灵思抽象 Shell 设计流程推出硬件开发套件( HDK ),将 DFX 技术推向更高水平,使其可以向最终客户交付预编译且时序收敛的 Shell,从而助力其促进协作、提高编译效率、降低许可成本。

如果要在 UltraScale+ 器件中执行手动眼扫描,重新排列程序会导致 PCIe 重新训练,降至第一代产品的速度,并停留在那里。

该设计咨询涵盖如下 UltraScale+ GTH/GTY 收发器问题,即 GTPOWERGOOD 在上电后可能无法断言有效。所有 UltraScale+ GTH/GTY 收发器中均包含 *_delay_powergood.v 模块。

了解全新的 16nm Artix® UltraScale+™ FPGA 系列和 Zynq® UltraScale+ MPSoC ZU1 器件,以超紧凑的封装提供,可为成本敏感型的边缘和网络应用提供无与伦比的计算密度。

一图读懂赛灵思全新UltraScale+成本优化型产品组合

在读取 IBERT 的自适应环路代码时,出现了与 DMONITOROUT 的期望值不同的值。对于 UltraScale+ GTH 收发器而言,签名了一些 RX 均衡自适应环路。用户指南的数字监控器 (DMON) 部分向用户展示了如何读取自适应环路的当前状态。

本视频围绕 UltraScale 和 UltraScale+ 架构,回顾了 DFX 布局规划基本信息;并提供了通过创建更优化的布局规划来改善设计结果的策略和技巧。