Vivado Versal 在连接多个 NOC 的情况下出现写/读访问阻塞

judy 在 周四, 06/01/2023 - 15:20 提交

对 Versal 设计使用 Vivado DFX 时出现硬件故障,我怎样才能避免这种情况?

对 Versal 设计使用 Vivado DFX 时出现硬件故障,我怎样才能避免这种情况?

本文将演示如何在 Versal AI Core 系列 VCK190 评估套件上从 USB 辅助启动模式启动 Linux

通信服务提供商往往采用无源光网 (PON) 为最终用户带来高速和低成本的光纤接入

了解 Versal 器件功耗估计从 XPE 迁移到 PDM 的简易迁移路径

在 CIPS GUI 中已对 Versal System Monitor 过热 (OT) 告警进行了说明

要为 Versal 的多个Quad创建收发器设置,建议从 Transceiver Bridge IP 开始

通过 IP integrator 选中多个 NoC site 时,不会在整个实现过程中遵循这些约束

如果 route_design 多次运行且在硬件中不切换路径

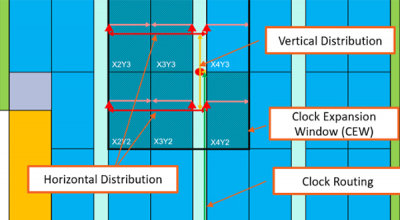

适用于 SSIT 的 Versal Fmax 取决于时钟拓扑结构扩展范围