Vitis 统一软件平台文档

judy 在 周三, 12/20/2023 - 10:26 提交

本用户指南涵盖了 Vitis 入门、使用 Vitis Unified IDE、Bootgen 工具

本用户指南涵盖了 Vitis 入门、使用 Vitis Unified IDE、Bootgen 工具

演示如何利用优化指令和 HLS 分析功能来高效驾驭各种 AMD 自适应 SoC 及 FPGA 产品的快速解决方案

Vitis Vision库中的内核在 Xilinx Vitis工具套件中进行了优化和支持

本文将在 Vitis™ 分析器中详解编译汇总文件,其中提供了有关编译的大量实用信息。

2023.1 版本提供了增强的工具,支持基于 AIE 的 DSP 设计的实现

本文是学习赛灵思 Zynq UltraScale+ MPSoC 5EV过程中写的笔记

在Vitis调试kernel过程中,用户可以在先行通过SW_EMU和HW_EMU测试

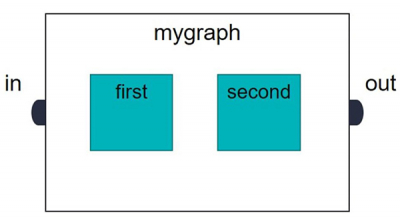

本文将进一步深入讲解工程内的 AIE graph