DFX流程(2)——非项目模式下的DFX

judy 在 周三, 11/23/2022 - 10:09 提交

Vivado同时支持在工程模式以及非工程模式中使用DFX流程,这里我们先从非工程模式开始介绍。

Vivado同时支持在工程模式以及非工程模式中使用DFX流程,这里我们先从非工程模式开始介绍。

vivado软件切换使用modelsim仿真时,如果出现如下图所示情况

本文主要介绍三个部分:DFX的基本流程、AS的环境搭建、AS的具体执行

Abstract Shell最大的优势是除第一次外,后续可以减少bit的生成时间

在Windows下Vivado默认使用的是2线程,编译较慢。可改为32线程使Vivado可使用更多计算机资源,以加快编译速度

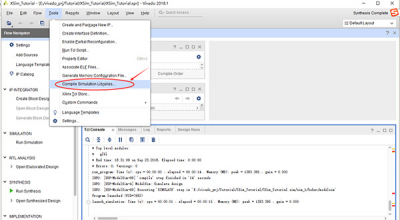

本文将介绍如何在Vivado中将代码编辑器绑定为第三方编辑器——Vscode

Vivado® Design Suite 可提供围绕 IP 的设计流程,支持您将来自各种设计的 IP 模块添加到自己的设计中

在使用vivado的过程中,如何添加设计文件?

书本中对于RAM的三种操作读优先级、写优先和保持使用等效的verilog来描述

在Vivado的界面中,有个RTL ANALYSIS->Open Elaborated Design的选项,可能很多工程师都没有使用过