Vivado-TLC5620驱动教程

judy 在 周五, 08/04/2023 - 10:16 提交

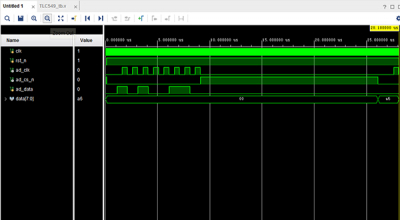

在FPGA处理完数字信号之后,我们有些情况下是需要将数字信号转变为模拟信号再输出的

在FPGA处理完数字信号之后,我们有些情况下是需要将数字信号转变为模拟信号再输出的

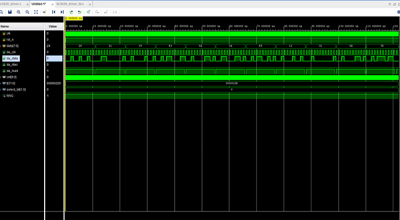

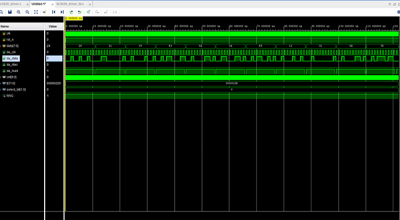

编写 HDL 通常是 FPGA 开发中耗时最少的部分,最具挑战性和最耗时的部分可能是验证

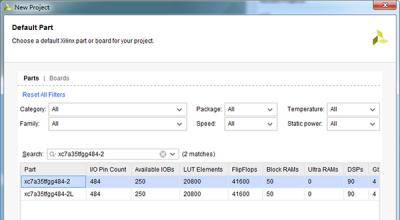

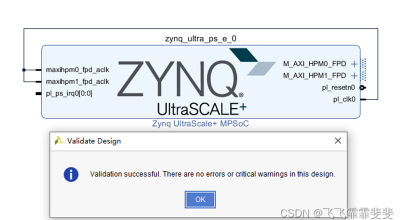

选择创建Block Design并命名,点击Add IP,并选择ZYNQ7

在生活中,数模转换的例子到处可见。但是在我们做FPGA设计时

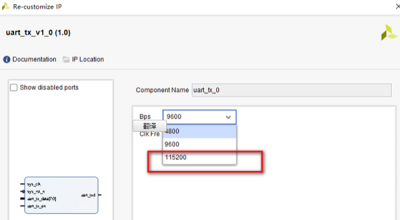

UART即通用异步收发器,是一种通用串行数据总线,用于异步通信

模块复用是逻辑设计人员必须掌握的一个基本功,通过将成熟模块打包成IP核

本文说明如何向Block Design添加.v文件模块

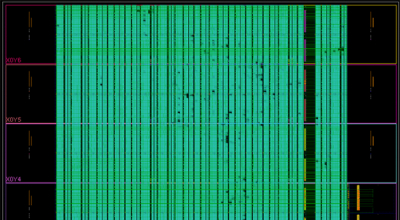

FPGA综合与布线效率研究

在设计规模和复杂性不断增长的世界里,SoC 和 FPGA 设计需要以更低功耗提供更高性能

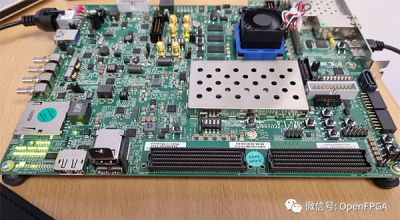

在xilinx zcu104开发板中,可以对FMC的电压进行调整,从而调整了FMC引脚的输出电压