利用Vitis开发基于ZCU106的神经网络加速器(一)——Vitis概述及XRT编译

guanxiao_505740 在 周一, 07/26/2021 - 14:45 提交

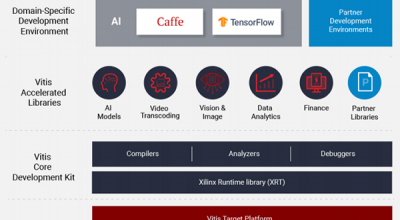

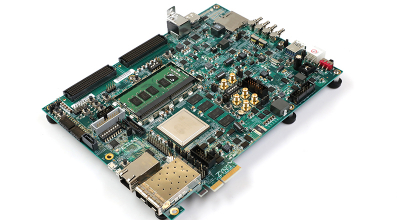

毕设要用到Xilinx家的ZCU106这块板子,了解到最近Xilinx统一了Vivado,XilinxSDK,并集成了常用开源IP核,推出了Vitis统一软件平台,使我们不再需要关注底层的Verilog实现,因此尝试使用Vitis开发一个神经网络加速器,作为毕设的基础。

毕设要用到Xilinx家的ZCU106这块板子,了解到最近Xilinx统一了Vivado,XilinxSDK,并集成了常用开源IP核,推出了Vitis统一软件平台,使我们不再需要关注底层的Verilog实现,因此尝试使用Vitis开发一个神经网络加速器,作为毕设的基础。

现在大规模FPGA的bitstream比较大导致板卡从上电到FPGA配置完成的时间远远超过100MS的要求,从而电脑端无法正常识别到PCIE设备。为此Xilinx的PCIE Tandem功能是专为满足PCIe设备在100ms之内枚举起来要求而设计的。

MPSoC的MAC支持1588。在Linux Kernel的配置项中使能CONFIG_MACB_USE_HWSTAMP,并在Linux rootfs添加Linux ptp/ethtool,就可以运行1588的软件命令ptp4l。

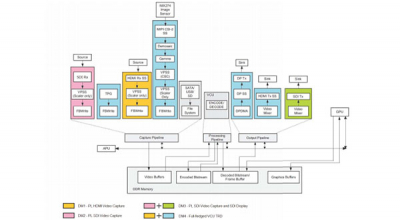

Xilinx提供超低延时编解码方案,在ZCU106单板上可以验证。文档MPSoC VCU TRD 2020.2 Low Latency XV20 提供了详细命令。缺省情况下,编码使用的是PS DDR。如果PS DDR已经被其它应用占用,也可以让编码使用的PL DDR。在VCU TRD 2020.2的例子zcu106_llp2_xv20基础上,做如下更改,可以实现使用PL DDR编码。

Xilinx提供超低延时编解码方案,在ZCU106单板上可以验证。文档MPSoC VCU TRD 2020.2 Low Latency NV16 提供了详细命令。下面的命令,能表现得更加稳定。

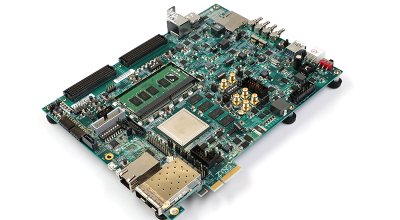

ZU+MPSOC器件在汽车电子、工业控制、机器视觉、智能安防、智慧城市等行业中已经有着广泛的应用,三年前在做一个ZCU106开发板的TRD(Target Reference Design)向用户自研板卡移植HDMI设计时,遇到了一些问题,我翻出之前的笔记整理成文,与大家分享。

了解如何使用 Zynq UltraScale + MPSoC 视频编解码器单元 (VCU) 中实现的基于感兴趣区域(ROI)的编码来最大化广播带宽。 我们将从广播带宽问题的简短讨论开始, 然后展示使用 Xilinx 视频编解码器单元,将基于区域的编码作为解决方案。

嵌入式Linux系统中,Linux直接管理所有CPU。默认情况下,系统的目标是提高吞吐率,而不是实时性。为了保证实时性,可以根据应用场景,对CPU实行更加精确的控制。常见的办法有,进程CPU隔离、CPU亲和、中断CPU亲和、进程优先级。

测试环境:Xilinx ZCU106 单板

Xilinx VCU TRD2020.1

Linux 内核配置:根据文档Docker on Zynq Ultrascale+ (Xilinx Yocto Flow),在PetaLinux工程的文件project-spec/meta-user/recipes-kernel/linux/linux-xlnx/user.cfg里添加下列配置项。

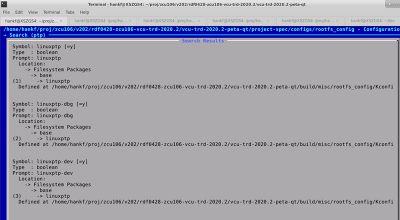

Xilinx VCU TRD 集成了图像和视频编解码功能,生成的根文件系统比较大,2020.1的rootfs.cpio.gz大约有114MB。工程师可以根据自己需要裁剪,减少根文件系统大小。

在Ubuntu下,解压rootfs.cpio.gz,得到rootfs.cpio,再解压,得到就是文件了。