ZYNQ 读写SD卡——FPGA Vitis篇

judy 在 周二, 06/27/2023 - 09:31 提交

本实验介绍如何使用Xilinx ZYNQ芯片在SD卡上读写文件

本实验介绍如何使用Xilinx ZYNQ芯片在SD卡上读写文件

同学们在学网络课程的时候都知道,除巨帧外,常见的以太网帧的长度范围是64字节到1518字节,并且因为最初总线型半双工的组网原因,人们制定了CSMA/CD协议,规定了以太网中最短帧为64字节。然而,互联网的发展日新月异,今天的网络早已不是当初的半双工模式

部分硬件设计中需要CPU完成对电路寄存器的配置,为了完成Zedboard对FPGA上部分寄存器的配置功能,可以在PS单元(处理器系统)上运行裸机程序(无操作系统支持)完成和PL单元(FPGA部分)的数据交互功能,此时PS单元更像单片机开发;另一种方法是PS单元运行Linux操作系统,通过驱动程序和应用程序......

首先要说明的是,往zedboard上移植opencv跟我们平时在pc上安装opencv的过程不同。毕竟zedboard是嵌入式平台很多东西都要删减,而且zedboard官方移植的linux不带图形界面,我们要自己在命令行下配置环境

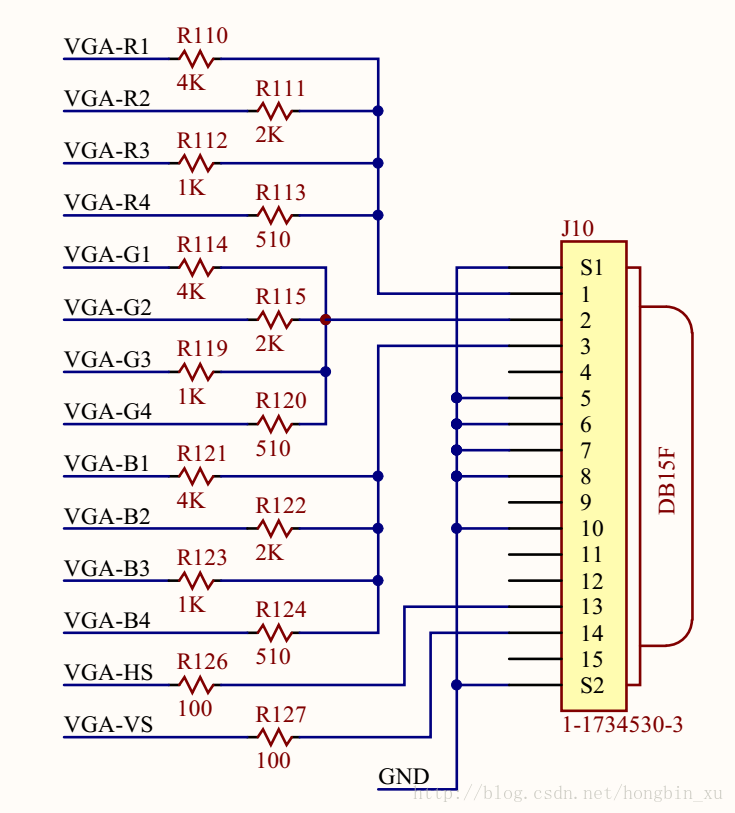

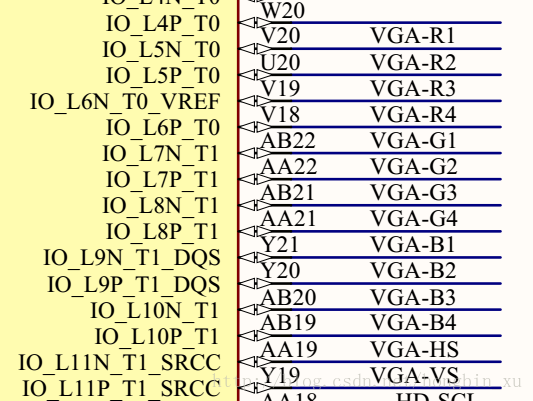

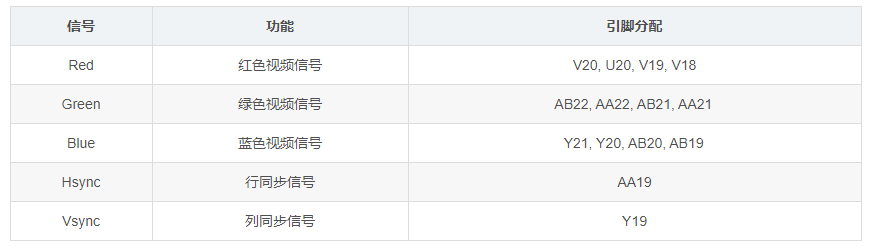

VGA硬件接口

到zedboard官方给出的原理图中查看:

RGB信号,各四位;这里的设计是使用了电阻分压模拟了DAC芯片实现了4X4X4的RGB信号,如果要更好的显示效果还是建议使用专门的DAC。

上面给出了所有的引脚分配。

VGA时序分析

zynq 的内嵌了 XADC,可以用来采集电压;

Temp:芯片温度

VCCINT: 内部PL核心电压

VCCAUX: 辅助PL电压

VCCBram: PL BRAM电压

VCCPInt: PS内部核心电压

VCCPAux: PS辅助电压

VCCDDR: DDR RAM的工作电压

VREFP: XADC正参考电压

VREFN: XADC负参考电压

1、新建工程,添加block design。添加zynq7 processor和xadc模块。

2、Run Block Automation后会自动配置zynq7处理器;Run Connection Automation 会自动将模块进行连接,将xadc模块挂载在axi总线下,这样xadc的相关寄存器会映射到处理器的内存(DDR)上。自动添加的两个模块,一个用于管理全局复位,一个用于同步axi总线。

Zynq7000 系列芯片有 54 个 MIO(multiuse I/O), 它们分配在 GPIO 的 Bank0 和Bank1 隶属于 PS 部分, 这些 IO 与 PS 直接相连。 不需要添加引脚约束, MIO 信号对 PL部分是透明的。 所以对 MIO 的操作可以看作是纯PS 的操作

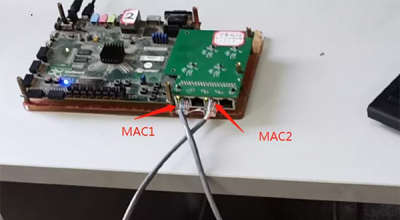

Zynq最核心的设计理念就是软件加硬件,即PS+PL。通过软硬件协同设计,结合了FPGA与双arm9内核,对于嵌入式拥有极大的优势。整个片上系统主要使用资源:ZYNQ系列FPGA XC7Z020、2片DDR、串口芯片(USB转UART)。Zedboard板子自带了这些资源,不需要另外添加模块。

文件系统用的Koheron提供的ubuntu16.04,将镜像文件解压后可以直接使用文件系统,具体使用命令的命令是fdisk 和mount