一、用HLS生成一个定制IP(加速器)

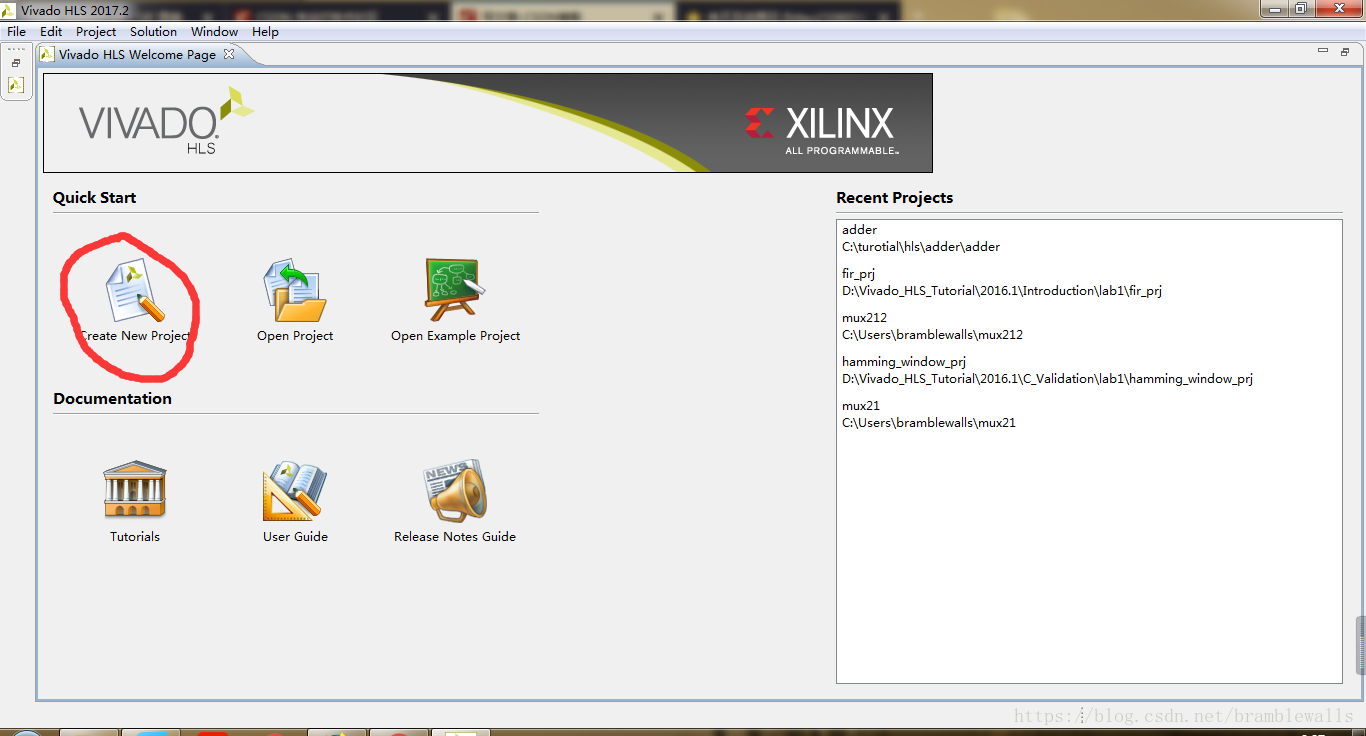

(1)首先打开vivado hls,本人的版本是2017.2,点击创建一个新工程。

(2)设置工程名和路径,顶层函数设置为add,创建一个新的C++程序,名字叫做adder.cpp,不用在testbench中添加文件。

选择板子的时候搜索xc7z020clg400-1,这是PYNQ的板子号,选择完成。

(3)在左侧的菜单栏里选择Source->adder.cpp,在里面编写如下代码:

void add(int a, int b, int& c) {

#pragma HLS INTERFACE ap_ctrl_none port=return

#pragma HLS INTERFACE s_axilite port=a

#pragma HLS INTERFACE s_axilite port=b

#pragma HLS INTERFACE s_axilite port=c

c = a + b;

}

这是一个简单的加法器,前面的宏定义是为了让运算并行,详细情况可以参考HLS设计的官方文档。

(4)完成之后我们可以在左侧菜单里选择solution1->impl->ip->drivers->add_v1_0->src->xadd_hw.h

不同的HLS版本可能位置不一样,如果没找到就换个位置找一下

在这个文件中我们可以找到a,b,c的地址,我们之后能够通过地址传值,读值

这里a为0x10,b为0x18,c为0x20

(5)下载PYNQ-Z1板卡文件,地址https://github.com/cathalmccabe/pynq-z1_board_files,

下载pynq-z1.zip,解压到C:\\Xilinx\Vivado\2017.2\data\boards\board_files里

二、在vivado中设计一个overlay

(1)打开vivado 2017.2,创建一个工程,选择板子的时候,选boards,在其中选择PYNQ-Z1

(2)在左侧导航中选择create block design

(3)在工作框中点击加号添加ZYNQ7 Processing System添加到工作面板中,然后点击Run Block Automation

(4)在菜单栏中选择tools->settings->ip->repository

点击加号,选择c:\tutorial\hls\adder把自己设计的IP添加进来,改名字为scalar_add

再点击Run Block Automation,结果如下

(5)在source栏中右键选择design sources->design_1(design_1.bd)右键选择create HLD wrapper

6)等wrapper完成之后选择generate bitstream生成bit文件

(7)生成bit文件之后点击file->export->export block design生成tcl文件

三、在Python中测试ip

在C:\tutorial\vivado\project_1\project_1.runs\impl_1中找到design_1_wrapper.bit文件拷贝到project_1文件夹下

将design_1.tcl文件和design_1_wrapper.bit文件改名为adder.tcl和adder.bit。将他们考到PYNQ-Z1板子的overlay目录下

使用jupyter notebook使用python对我们自己的ip进行测试,结果如上所示。

使用继承的read和write函数操作地址,进行传值和读值。

本文参考http://pynq.readthedocs.io/en/latest/overlay_design_methodology/overlay_...

---------------------

作者:bramblewalls

来源:CSDN

原文: https://blog.csdn.net/bramblewalls/article/details/80045922