虽然在图像数据流水线中已包含行列坐标,但是一些算法由于其本身的设计必须由行有效信号 lv 重新生成行列坐标。

令图像的列数目为 COLS,行数目为 ROWS。

列坐标范围 0~(COLS-1)。

行坐标范围 0~(ROWS-1)。

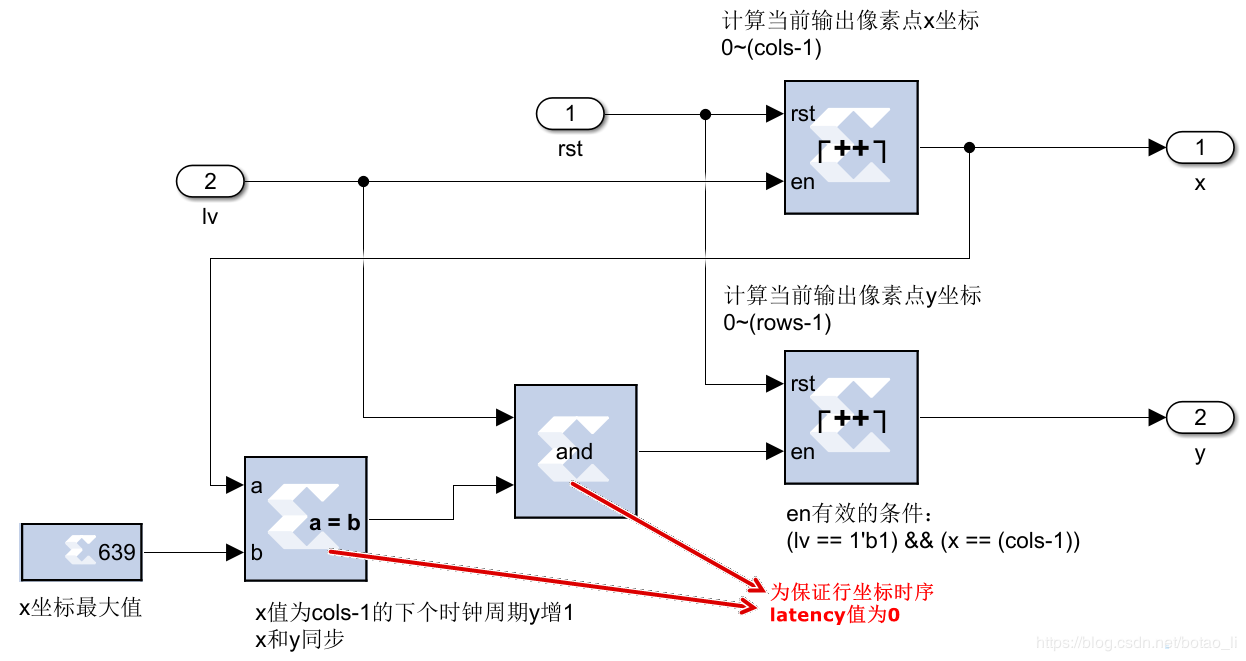

基本设计思想是使用 2 个计数器分别计算列坐标和行坐标,当列坐标计数器计数至最大列坐标时,行坐标值增 1 。

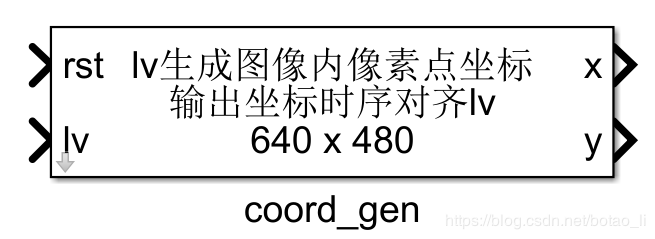

模块 Subsystem 封装后如下所示:

rst 用于复位坐标计数,lv 为输入的行有效信号,x 和 y 分别为输出的列坐标与行坐标。

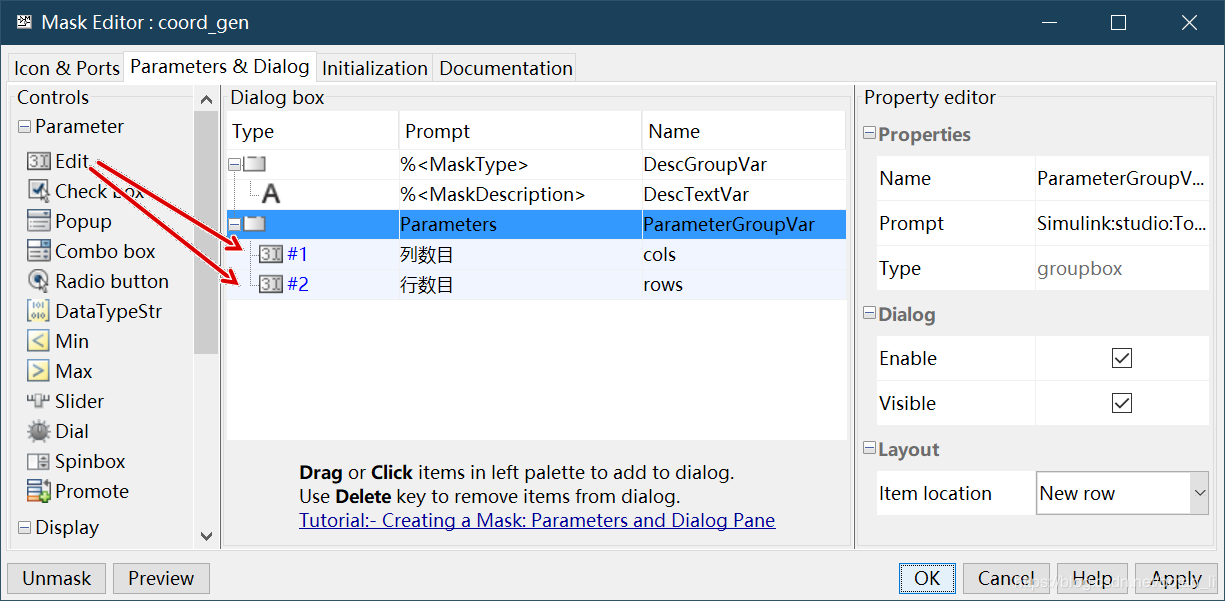

在 Subsystem 的 mask 中定义列数目 cols 变量和行数目 rows 变量:

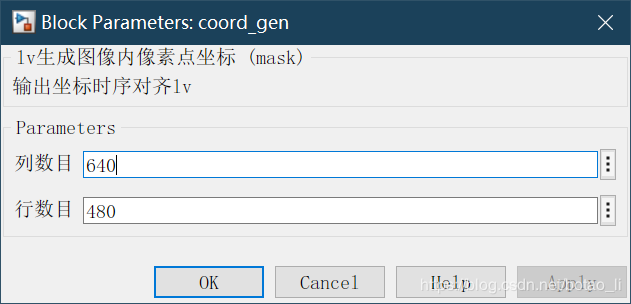

双击 Subsystem 弹出参数设置窗口:

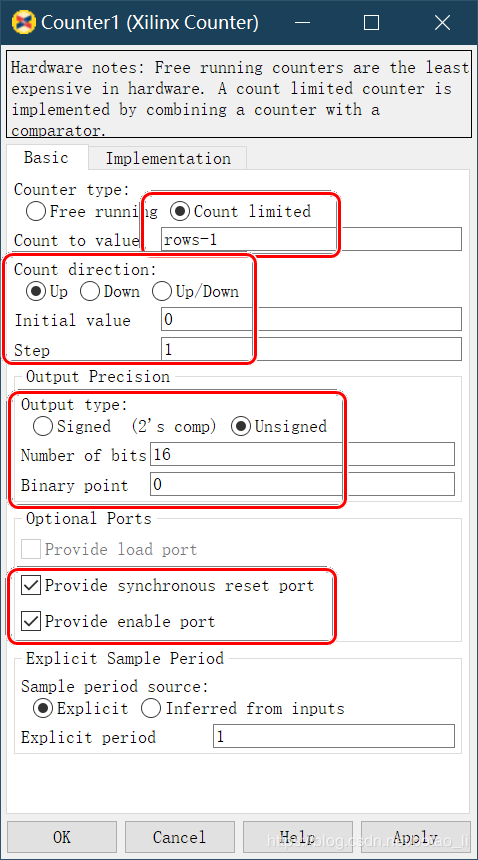

列坐标计数器的配置如下:

行坐标计数器配置如下:

完整设计:

版权声明:本文为CSDN博主「bt_」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/botao_li/article/details/100521277