浮点数与无符号整数转换

图像处理算法在 sysgen 中实现,大多使用定点整数计算,并且为了与图像算法原理一致,定点整数也仅限于无符号整数。

对于必须与小数相乘的算法,在 sysgen 实现时可以用乘以无符号整数后再进行截去低位的办法实现等效计算。但是如果小数计算的数值在不同情况下有多种不确定的数值,则无法用先乘法再截位的办法模拟,只能使用浮点数进行计算。

由此必须将定点无符号整数转化为浮点数,完成计算后将浮点数计算结果转化为定点无符号整数输出。

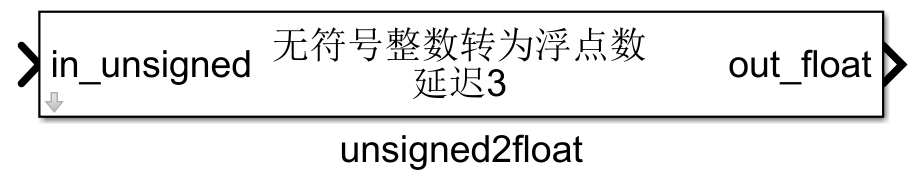

无符号整数转为浮点数

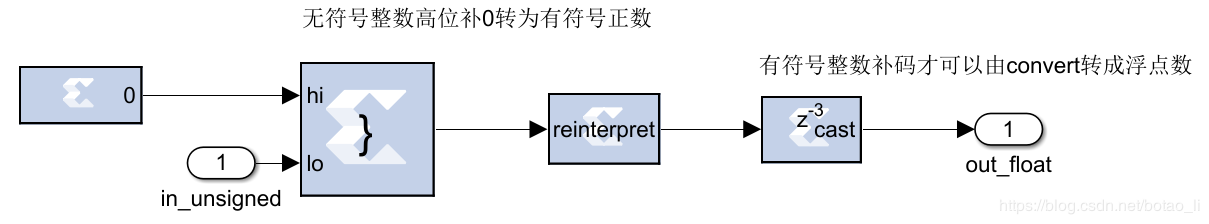

无符号整数转为浮点数的 Subsystem 封装如下:

in_unsigned 是输入的无符号整数,out_float 是数值相等的浮点数。

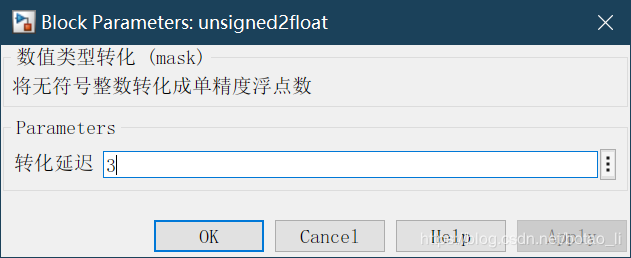

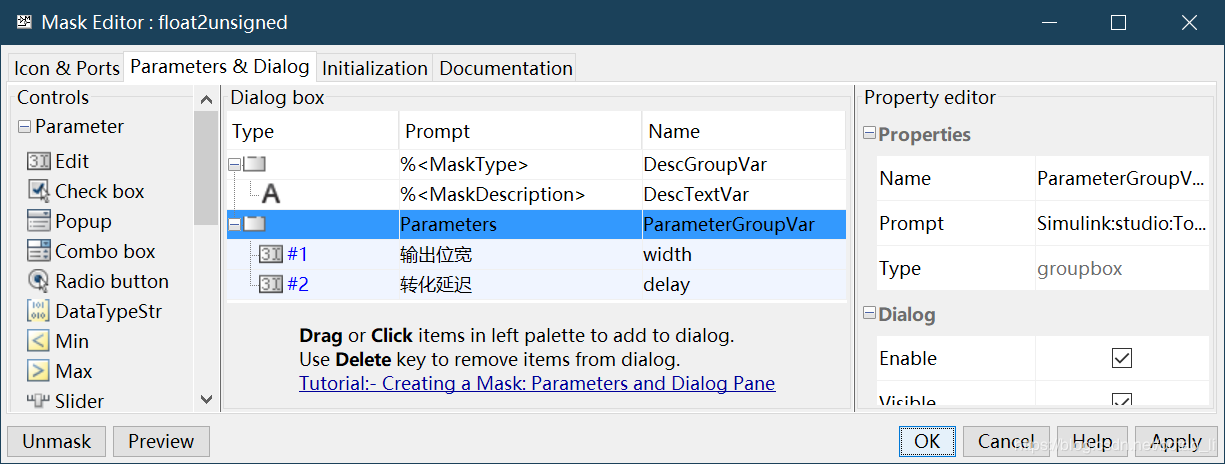

在 Subsystem 的 mask 中定义参数转化延迟 delay,方便计算流水线时序对齐:

双击 Subsystem 弹出参数设置窗口:

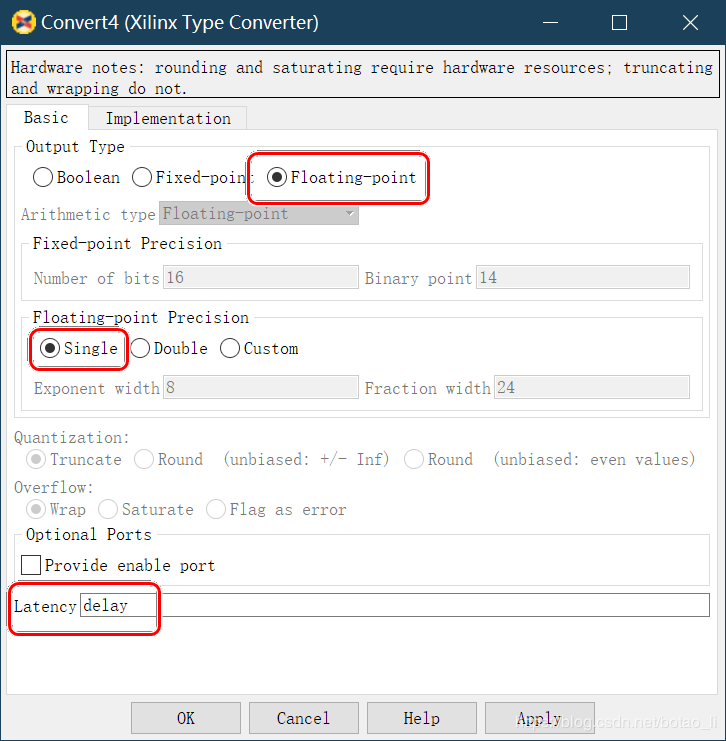

数值类型转化的功能主要由 Convert 模块实现,模块配置如下:

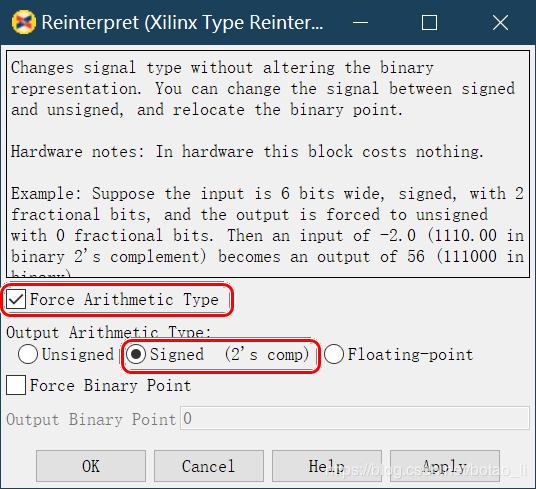

但是由于 Convert 模块只能将有符号整数转化为浮点数,因此输入的无符号整数需要由 Concat 模块经过高位补 0 再由 Reinterpret 模块解释为有符号整数(正数二进制补码)再送入整数转化为浮点数的 Convert 模块。

Reinterpret 模块的配置如下:

完整设计:

浮点数转为无符号整数

浮点数转为无符号整数的 Subsystem 封装如下:

in_float 是输入的浮点数,out_unsigned 是输出的无符号整数,在转化过程中如果输入浮点数值小于 0,则输出整数值为 0,如果输入浮点数值大于当前设置位宽的满量程值,则输出该满量程值。

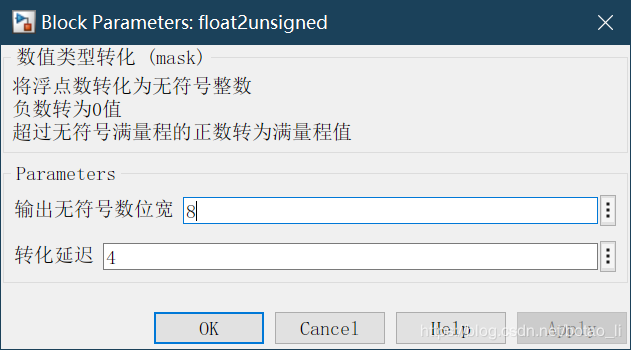

在 Subsystem 中定义参数输出位宽 width 和转化延迟 delay:

双击 Subsystem 弹出参数设置窗口:

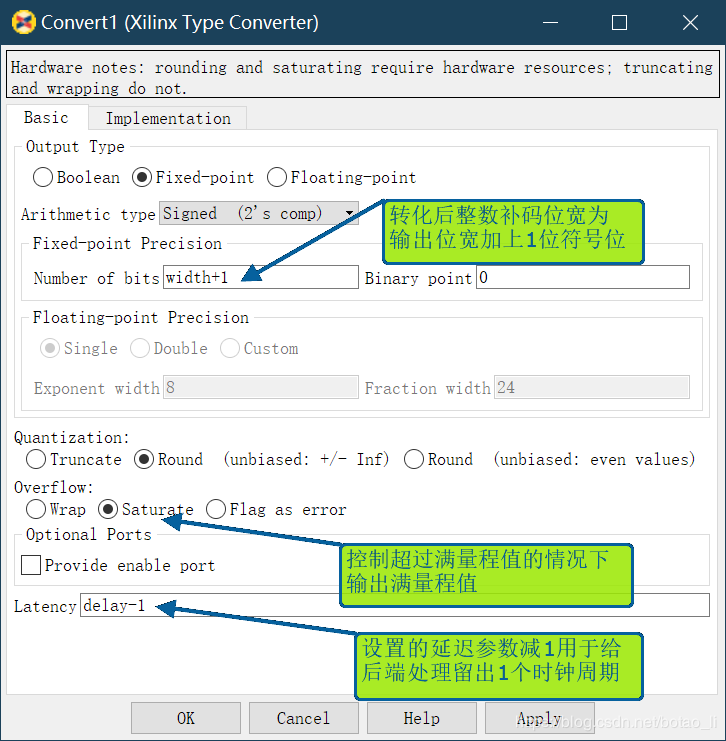

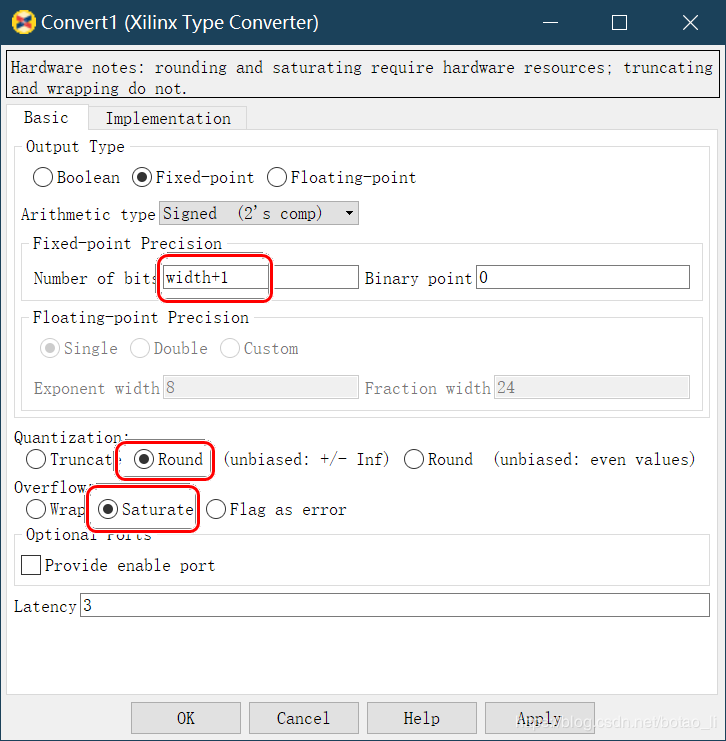

具体实现时,首先用 Convert 模块将浮点数转化为有符号整数补码,Convert 模块配置如下:

Convert 输出的有符号整数补码再经过 Convert 模块转化为无符号整数,第 2 级 Convert 模块配置如下:

完整设计:

正浮点数向下取整

在插值计算过程中,常常需要计算浮点数的坐标值,并且将该浮点值向下取整以找到邻近的坐标。这种情况下就可以使用正浮点数向下取整模块。

除了用于向下取整,得到输出的整数值后,输出值加 1 可以得到向上取整的结果,用输入浮点数减去向下取整的数值可以得到浮点数的小数部分。

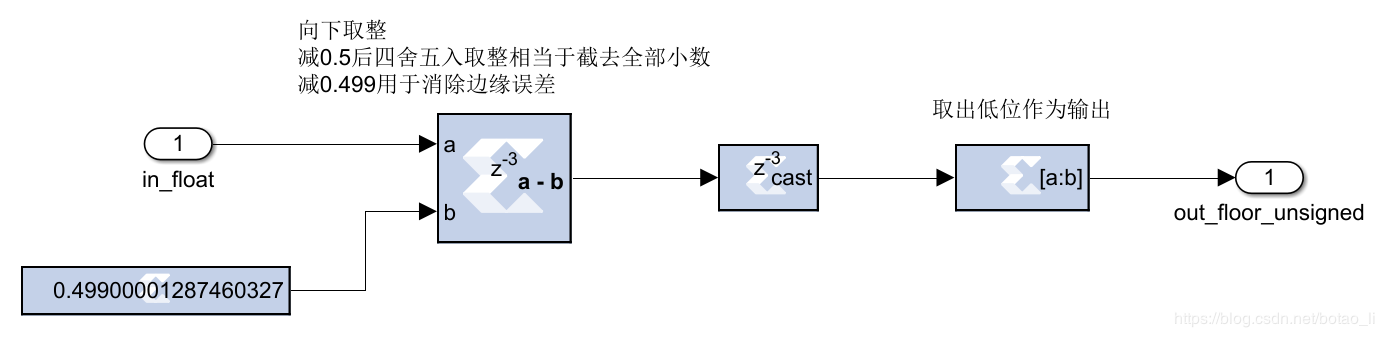

由于 Convert 模块将浮点数转为整数时只能使用 round 近似,因此向下取整的基本原理在于将正浮点数减去 0.5 后,再使用 round 进行四舍五入。

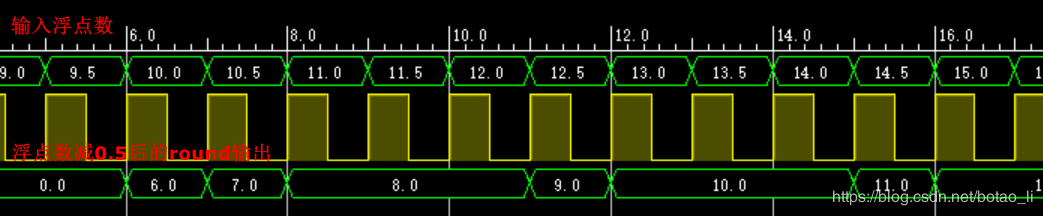

但是仿真发现,浮点数小数部分的 round 计算并非四舍五入,下图是输入浮点值减 0.5 后的round输出,延迟为 6:

图中可以发现 10.0、10.5、1.0 的输出值全部为 10,明显不符合预期。

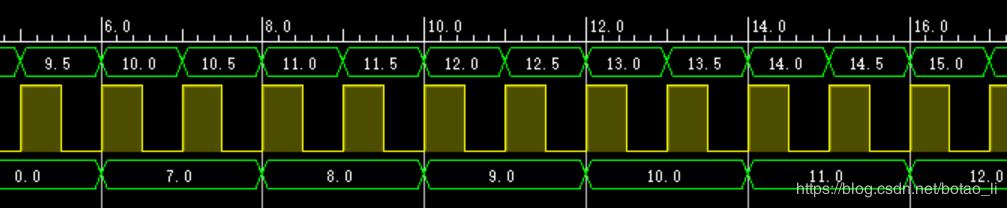

为了解决这个 round 错误,减 0.5 改成减 0.499,仿真输出正确:

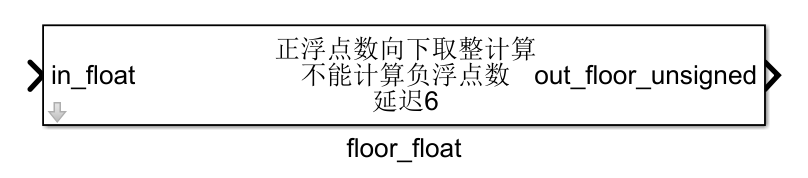

Subsystem 封装如下:

在 Subsystem 中定义输出无符号整数位宽:

完整设计:

Convert 模块的配置如下:

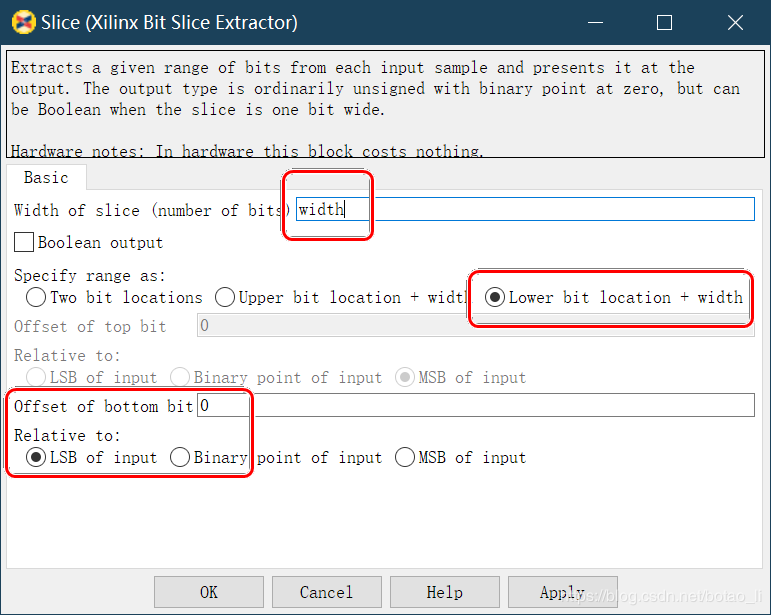

截取低位输出的 Slice 模块配置如下:

版权声明:本文为CSDN博主「bt_」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/botao_li/article/details/100521430